## High Frequency Link Current Estimation Based Control of Solid State Transformer

A thesis submitted in partial fulfillment for the award of the degree of

**Doctor of Philosophy**

by

Gourahari Nayak

Department of Avionics

Indian Institute of Space Science and Technology

Thiruvananthapuram, India

**April 2025**

**Certificate**

This is to certify that the thesis titled High Frequency Link Current Estimation Based

Control of Solid State Transformer submitted by Gourahari Nayak, to the Indian Institute

of Space Science and Technology, Thiruvananthapuram, in partial fulfillment for the award

of the degree of **Doctor of Philosophy** is a bona fide record of the original work carried out

by him/her under my supervision. The contents of this thesis, in full or in parts, have not

been submitted to any other Institute or University for the award of any degree or diploma.

Dr. Anindya Dasgupta

Associate Professor

Department of Avionics

**IIST**

Dr. N. Selvaganesan

Professor and Head

Department of Avionics

**IIST**

**Place:** Thiruvananthapuram

Date: April 2025

i

#### **Declaration**

I declare that this thesis titled *High Frequency Link Current Estimation Based Control of Solid State Transformer* submitted in partial fulfillment for the award of the degree of **Doctor of Philosophy** is a record of the original work carried out by me under the supervision of **Dr. Anindya Dasgupta**, and has not formed the basis for the award of any degree, diploma, associateship, fellowship, or other titles in this or any other Institution or University of higher learning. In keeping with the ethical practice in reporting scientific information, due acknowledgments have been made wherever the findings of others have been cited.

Place: Thiruvananthapuram Gourahari Nayak

**Date:** April 2025 (SC17D017)

This thesis is dedicated to my Parents and my Family . . .

### Acknowledgements

I express my sincere gratitude to my thesis supervisor, Dr. Anindya Dasgupta, for accepting me as his student and guiding me throughout this journey. His patience, constant support and valuable time have been instrumental in the completion of this thesis. His unwavering enthusiasm, passion and commitment to research continually inspire and motivate me. I am especially grateful to him for introducing me to an exciting research topic that holds significant contemporary industrial interest. Additionally, I extend my thanks to him for providing all the necessary hardware facilities required for the experimental work. His mentorship and encouragement have been pivotal to my academic growth and success.

I would like to express my heartfelt gratitude to the Doctoral Committee members Dr. Rajeevan P. P., Dr. R. Sudharshan Kaarthik, Dr. Deepak Mishra, Dr. N. Selvaganesan, Dr. Manoj B. S. and Dr. Kaushik Mukherjee. Their invaluable guidance and insightful feedback have played a crucial role in shaping my research work. I deeply appreciate their time and effort throughout this journey. I feel privileged to have been part of the exceptional coursework provided by Dr. Anindya, Dr. Rajeevan, Dr. Sudharshan, and Dr. Harsha Simha M.S. at IIST.

I consider myself incredibly fortunate for having the opportunity to work in an exceptional Power Electronics Lab at IIST. Dhanya madam's unwavering support has been an absolute blessing. Serving as a maternal figure in my life, her love and affection has been instrumental in helping me navigate through challenging times. I would also like to extend my gratitude to all other faculty and staff members for their direct and indirect support.

It has been an absolute honour to share moments with colleagues like Vidya and Prasoon. This journey would not have been as fulfilling without the unwavering support of my incredible lab mates: Archit, Ranjith, Yadavendra, Hari Krishna, Arpita, Pragya, Dha-

rani, Deeksha, Chandrakant, Ajmal and Anupam. A big thanks to them for their time and support. I have learnt a great deal from them and their presence has greatly enriched my journey.

During my time in IIST, I have been fortunate to cross paths with remarkable friends like Pramod, Deba, Shiv, Avinash, Gaurab and Danish. I am grateful to them for making my stay in the hostel more enjoyable.

The most significant of all, I extend my deepest gratitude to my Mother (Ahalya Nayak), Father (Gobardhan Nayak), my beloved Sister (Madhusmita Nayak), Sanabapa (Dinabandhu Nayak), Tiki mausi (Subhalaxmi Nayak) and my wife (Pallavi Nayak) for their unwavering love, encouragement and support throughout my journey. Their endless sacrifices, understanding and belief in me have been the pillars of my strength. If this work or my mere life holds any significance in this infinite world, it is solely because of the unfathomable love, boundless blessings and relentless inspiration they have bestowed upon me.

Finally, I humbly express my gratitude before the Almighty for his guidance and blessings, which have illuminated my path and provided strength throughout this journey of life. His serene presence has always been my constant source of solace.

Gourahari Nayak

#### **Abstract**

The pressing need to address climate change demands substantial transformations within the power and transportation sectors, centering on the adoption of sustainable energy sources. A crucial aspect of this transition is the decarbonization of these sectors. Traditional line frequency transformers (LFTs) are inadequate for handling the intermittent, dynamic and bidirectional power flows introduced by renewable energy sources and electric vehicles (EVs). Solid State Transformer (SST) is emerging as a promising solution owing to their sophisticated control functionalities, compact form factor and adeptness to manage these new demands in modern power distribution systems. At the heart of the SST lies the Dual Active Bridge (DAB) converter, acting as the central power processing unit orchestrating the power flow. The critical component within the entire system is the high-frequency link (HF-link) transformer of DAB. Therefore, an effective control strategy must acquire HFlink current information to provide overcurrent protection and safeguard this transformer against saturation, ensuring system stability under varying conditions. Many reported control techniques rely on measuring HF-link current, requiring a high-bandwidth (HBW) current sensor, high sampling frequency ADC and additional signal processing circuitry, hindering overall cost-effectiveness and compact design. Many other reported current control methods use a reduced-order dynamic model that excludes HF-link current as a system state variable, failing to provide any information about the critical high frequency transformer.

This thesis attempts to contribute to a broader endeavour by developing a HBW current sensorless control strategy based on state estimation. Its goal is to control the power flow and provide pre-emptive overcurrent saturation protection by gathering the HF-link current information through estimation, instead of directly measuring it.

Additionally, this thesis addresses the key challenges associated with the modular configuration of SST by extending the developed control strategy for a single DAB module to modular SST configurations. Modularity allows for scalability, simplified maintenance, design flexibility, system reconfiguration and enhanced reliability through redundancy. This thesis considers two types of modular configurations: input-series-output-parallel (ISOP) and input-parallel-output-parallel (IPOP). It is inevitable to have parameter mismatches across the cells of modular SST, especially unequal leakage inductances of HF-link transformers, which invariably lead to unbalanced DC-link voltages and unequal power distribution. While many reported control methods focus on power balance control strategies, this thesis attempts to establish the need for flexible power sharing control capable of facilitating equal power sharing, controlled unequal power sharing and zero power sharing (plug-in/plug-out operation) depending on normal or contingency situation.

To meet the set of objectives, efforts are directed towards developing HBW current sensorless control method, relying on the estimation of the fundamental component of HF-link current, to achieve flexible power sharing control in both modular ISOP and IPOP SSTs. Additionally, the process of parameter identification for the HF-link inductance is explored to effectively tackle parametric variations. In the IPOP configuration, it is attempted to achieve unity power factor (UPF) operation of multiple parallel modules connected to grid, using a single low bandwidth current sensor.

The developed methods are validated through simulations and extensive experimental results. The proposed solutions in this thesis have the potential to enhance reliability, achieve seamless power flow and reduce cost of the SST system.

## **Contents**

| Li | st of I | Figures                                            | XV   |

|----|---------|----------------------------------------------------|------|

| Li | st of ' | Tables                                             | xxii |

| Ał | obrev   | iations                                            | XXV  |

| 1  | Intr    | oduction                                           | 1    |

|    | 1.1     | Background                                         | 1    |

|    | 1.2     | The Solid State Transformer                        | 4    |

|    | 1.3     | Motivation of the Thesis                           | 12   |

|    | 1.4     | Objectives of the Thesis                           | 20   |

|    | 1.5     | Thesis Outline                                     | 20   |

| 2  | Low     | Frequency Dynamic Model                            | 23   |

|    | 2.1     | Modeling of CMFEC                                  | 24   |

|    | 2.2     | Modulation Scheme of CMFEC                         | 30   |

|    | 2.3     | Modeling of OPDAB                                  | 30   |

|    | 2.4     | Validation Through Simulation                      | 41   |

|    | 2.5     | Concluding Remarks                                 | 48   |

| 3  | Env     | elope Tracking Based Control of DAB                | 49   |

|    | 3.1     | Reported Control Schemes and the Proposed Strategy | 50   |

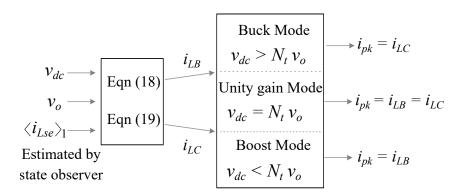

|    | 3.2     | Current Envelope Estimation Based Control               | 52  |

|----|---------|---------------------------------------------------------|-----|

|    | 3.3     | Correction Factor Inclusion                             | 60  |

|    | 3.4     | Results and Discussion                                  | 63  |

|    | 3.5     | Concluding Remarks                                      | 71  |

| 4  | Esti    | mation Based Flexible Power Sharing Control of ISOP SST | 72  |

|    | 4.1     | Requirement for Flexible Power Sharing Control          | 72  |

|    | 4.2     | Functional Comparison with Other Reported Schemes       | 74  |

|    | 4.3     | Voltage Balance Control                                 | 77  |

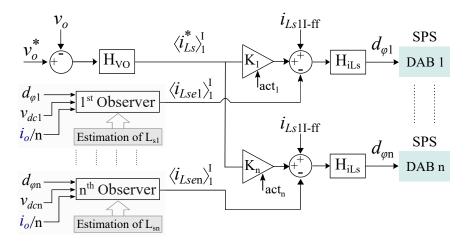

|    | 4.4     | Sensorless Power Balance Control                        | 82  |

|    | 4.5     | Results and Discussion                                  | 89  |

|    | 4.6     | Concluding Remarks                                      | 104 |

| 5  | Esti    | mation Based Flexible Power Sharing Control of IPOP SST | 106 |

|    | 5.1     | Requirement of an IPOP Configuration                    | 106 |

|    | 5.2     | Reported Control Schemes and the Proposed Strategy      | 108 |

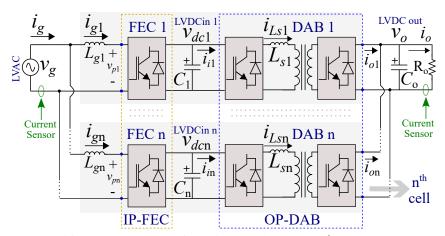

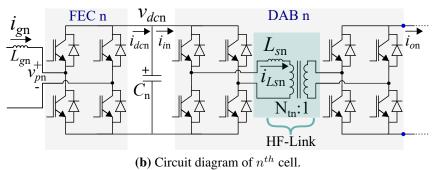

|    | 5.3     | IPFEC Stage Voltage Balance Control                     | 110 |

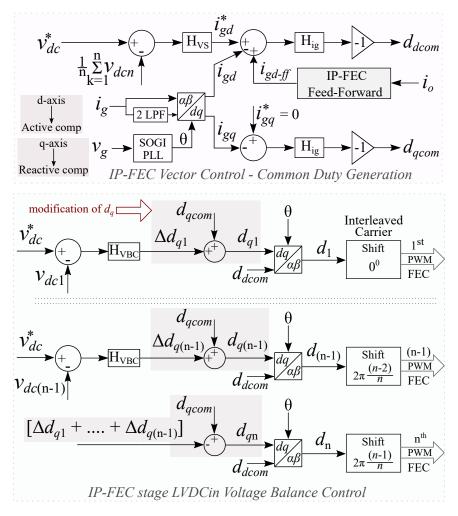

|    | 5.4     | OPDAB Stage Power Balance Control                       | 113 |

|    | 5.5     | Results and Discussion                                  | 120 |

|    | 5.6     | Concluding Remarks                                      | 130 |

| 6  | Con     | clusion                                                 | 131 |

|    | 6.1     | Conclusions and Contribution                            | 131 |

|    | 6.2     | Future Work                                             | 133 |

| Bi | bliogi  | raphy                                                   | 133 |

| Li | st of I | Publications                                            | 147 |

| Ap | ppendices                                                     | 149 |

|----|---------------------------------------------------------------|-----|

| A  | Theorems Associated with Properties of Complex Fourier Series | 149 |

| В  | Derivation of EFHA Model                                      | 151 |

# **List of Figures**

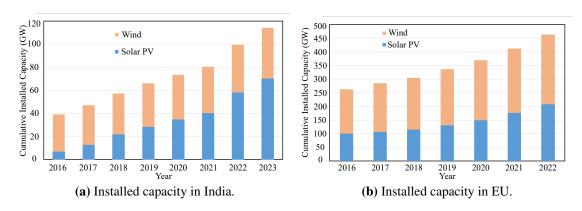

| 1.1  | Renewable energy (solar and wind) installed capacity                                    | 1  |

|------|-----------------------------------------------------------------------------------------|----|

| 1.2  | Emission from various sectors                                                           | 2  |

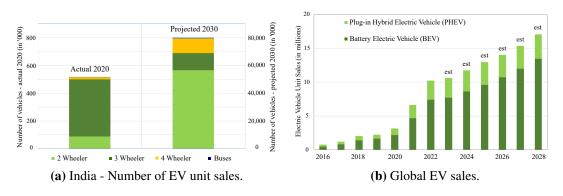

| 1.3  | Projected electric vehicle (EV) sale for this decade                                    | 2  |

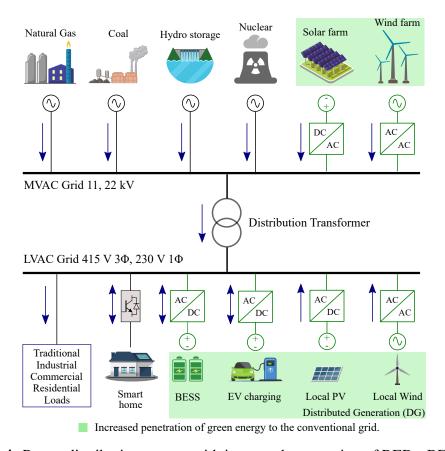

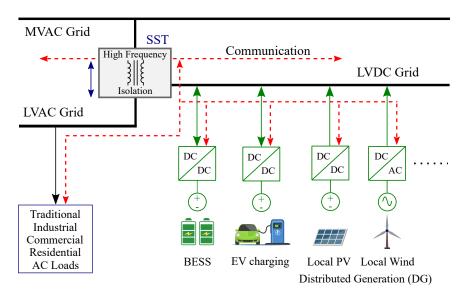

| 1.4  | Power distribution system with increased penetration of RERs, BESS, EVs.                | 3  |

| 1.5  | Envisioned future distribution grid with SST                                            | 5  |

| 1.6  | Power flow between main grid-microgrid and microgrid-microgrid                          | 7  |

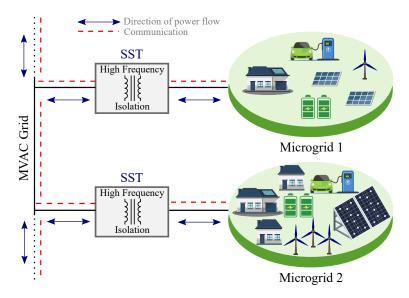

| 1.7  | Types of SST topology based on power conversion stages                                  | 7  |

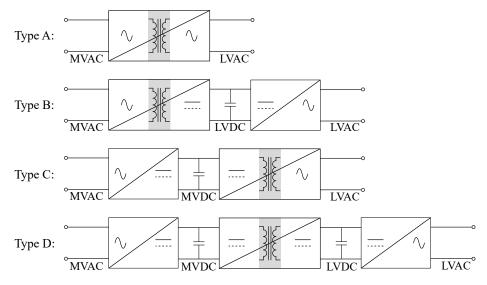

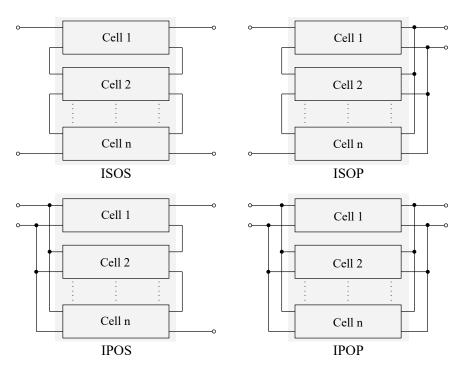

| 1.8  | Four types of series-parallel connected modular power conversion systems.               | 10 |

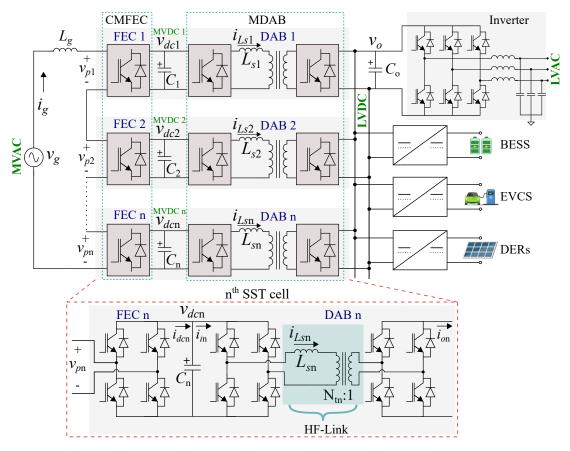

| 1.9  | Selected three stage modular ISOP Type D SST topology                                   | 12 |

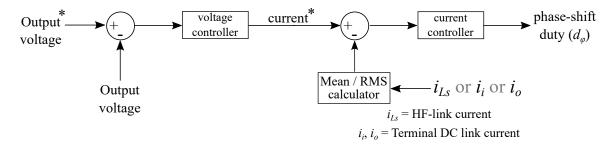

| 1.10 | Dual loop control of DAB converter                                                      | 13 |

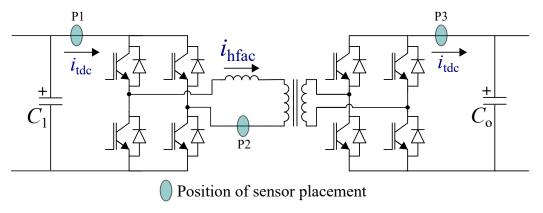

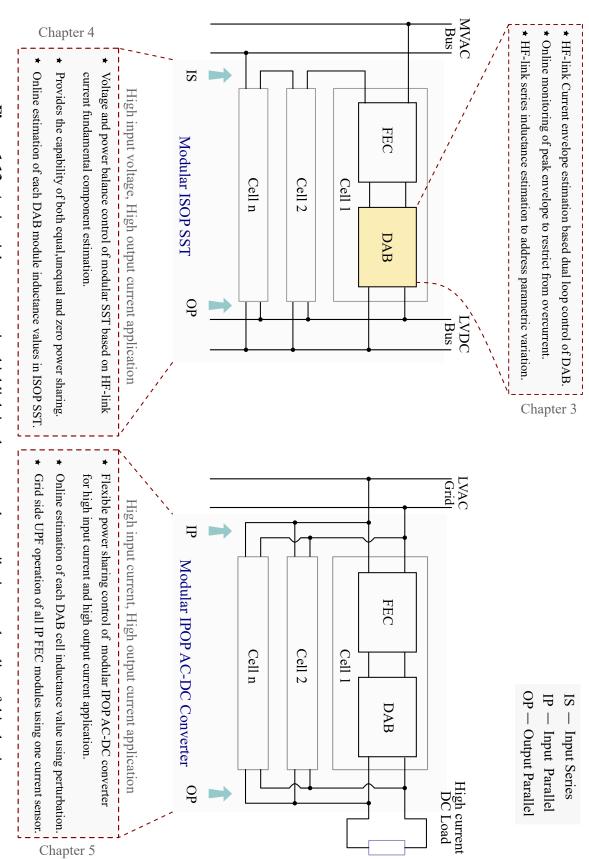

| 1.11 | DAB circuit showing position of current sensor placement                                | 15 |

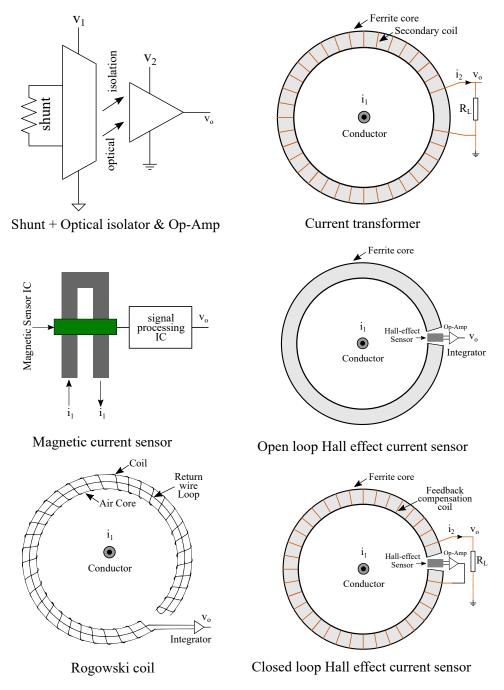

| 1.12 | Few examples of isolated current sensors                                                | 16 |

| 1.13 | A pictorial representation highlighting key research contributions and out-             |    |

|      | line of this thesis                                                                     | 22 |

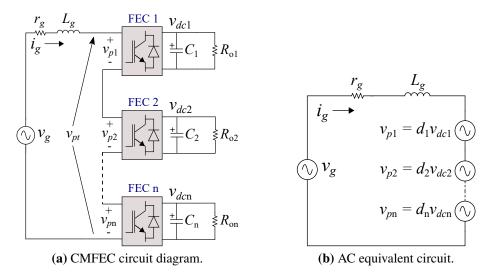

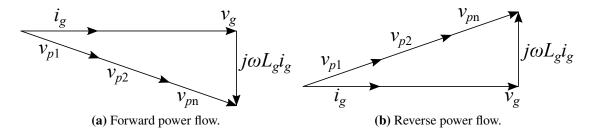

| 2.1  | CMFEC and its AC equivalent circuit                                                     | 23 |

| 2.2  | Phasor diagram of CMFEC for UPF operation                                               | 25 |

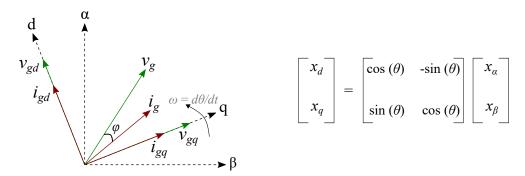

| 2.3  | Stationary $\alpha\beta$ to synchronously rotating $dq$ reference frame transformation. | 25 |

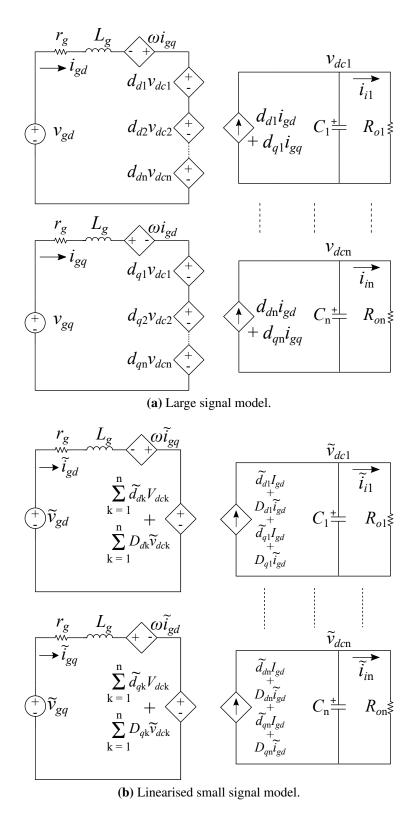

| 2.4  | Large signal and small signal model of CMFEC in $dq$ reference frame                    | 27 |

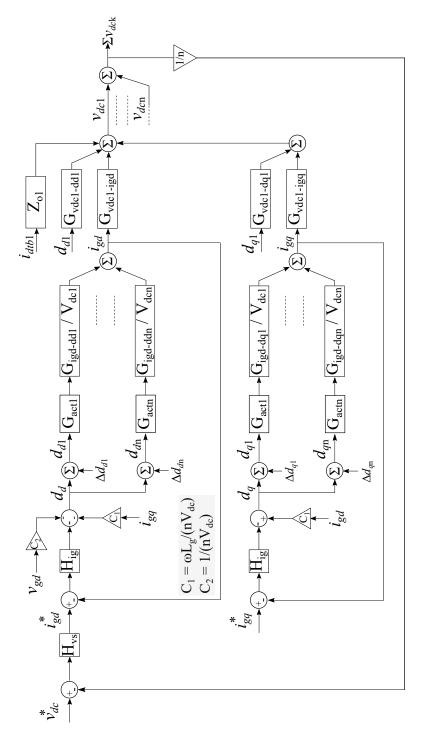

| 2.5  | Control diagram of CMFEC in $dq$ reference frame showing dual loop control.             | 29 |

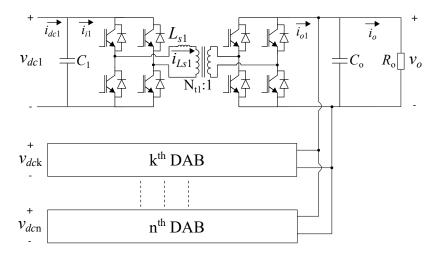

| 2.6  | Modular OPDAB circuit diagram                                                                                                                                                                                                                                                                                                                              | 31 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | Large signal and small signal model of OPDAB stage                                                                                                                                                                                                                                                                                                         | 33 |

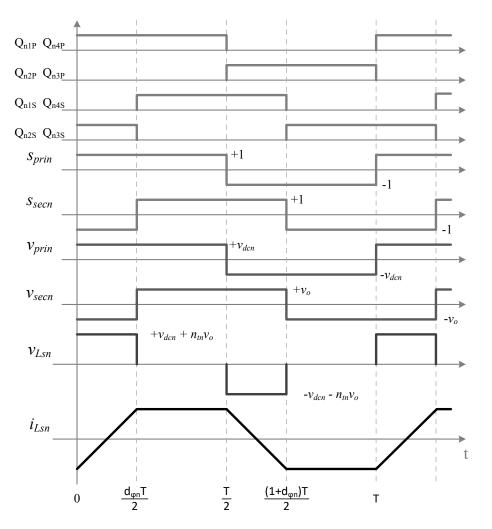

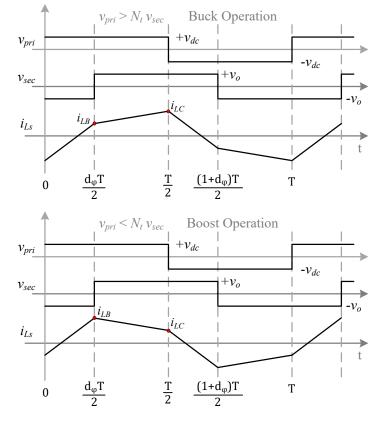

| 2.8  | DAB waveforms during one switching period                                                                                                                                                                                                                                                                                                                  | 35 |

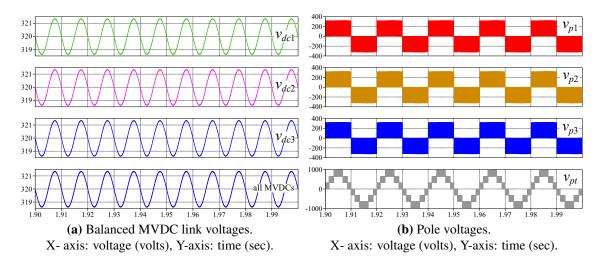

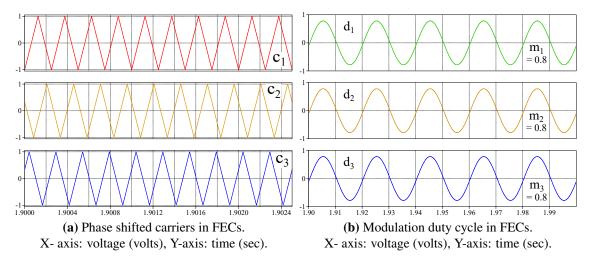

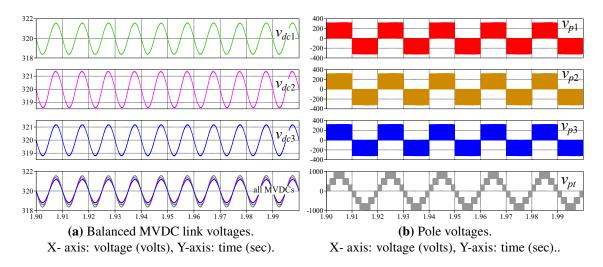

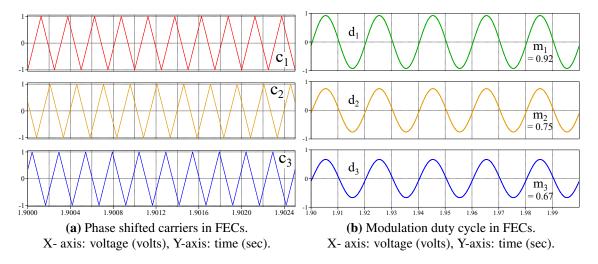

| 2.9  | Simulation results showing balanced MVDCs and the pole voltages with same load connected to each FEC module output ( $R_{o1}=R_{o2}=R_{o3}$ )                                                                                                                                                                                                              | 42 |

| 2.10 | Simulation results showing phase shifted carriers and individual modulation duty cycles with same load connected to each FEC module output $(R_{o1}=R_{o2}=R_{o3})$                                                                                                                                                                                        | 42 |

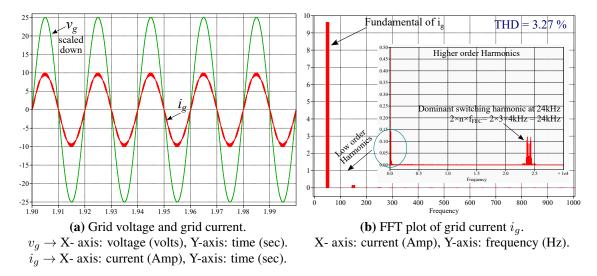

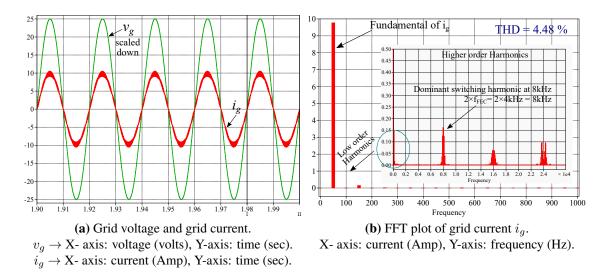

| 2.11 | Simulation result showing grid side UPF operation and FFT plot of current drawn from grid with same load connected to each FEC module output $(R_{o1} = R_{o2} = R_{o3})$                                                                                                                                                                                  | 43 |

| 2.12 | Simulation results showing balanced MVDCs and the pole voltages with 15% variation in load connected to each FEC module output ( $R_{o1} \neq R_{o2} \neq R_{o3}$ )                                                                                                                                                                                        |    |

| 2.13 | Simulation results showing phase shifted carriers and individual modulation duty cycles with 15% variation in load connected to each FEC module output $(R_{o1} \neq R_{o2} \neq R_{o3})$                                                                                                                                                                  | 44 |

| 2.14 | Simulation result showing grid side UPF operation and FFT plot of current drawn from grid with 15% variation in load connected to each FEC module output $(R_{o1} \neq R_{o2} \neq R_{o3})$                                                                                                                                                                | 44 |

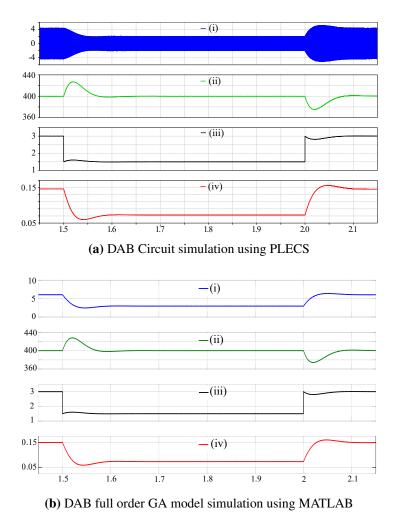

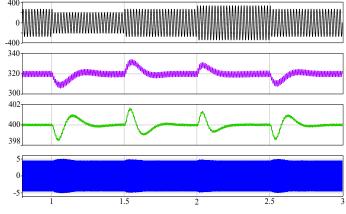

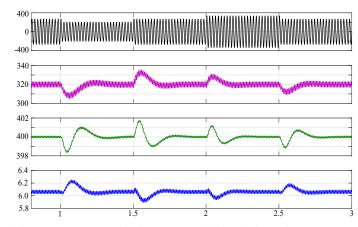

| 2.15 | Simulation results (a) With PLECS. Top trace: $i_{Ls1}$ , 2nd trace: $v_o$ , 3rd trace: $i_o$ , bottom trace: $d_{\varphi 1}$ . (b) With MATLAB. Top trace: $\langle i_{Ls1} \rangle_1$ , 2nd trace: $v_o$ , 3rd trace: $i_o$ , bottom trace: $d_{\varphi 1}$ . (c) Top trace: $i_{Ls1}$ with PLECS, Bottom trace: $\langle i_{Ls1} \rangle_1$ with MATLAB | 46 |

|      | , - · · · · · · ·                                                                                                                                                                                                                                                                                                                                          |    |

| 2.16 | Simulation results (a) With PLECS. Top trace: $v_g$ , 2nd trace: $v_{dc1}$ , 3rd                                    |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

|      | trace: $v_o$ , bottom trace: $i_{Ls1}$ . (b) With MATLAB. Top trace: $v_g$ , 2nd trace:                             |    |

|      | $v_{dc1}$ , 3rd trace: $v_o$ , bottom trace: $\langle i_{Ls1} \rangle_1$ . (c) Top trace: $i_{Ls1}$ with PLECS,     |    |

|      | Bottom trace: $\langle i_{Ls1} \rangle_1$ with MATLAB                                                               | 47 |

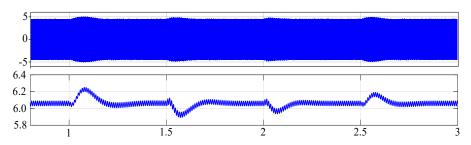

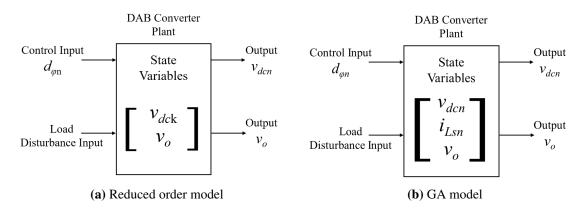

| 3.1  | Block diagram highlighting difference between reduced order and GA model.                                           | 50 |

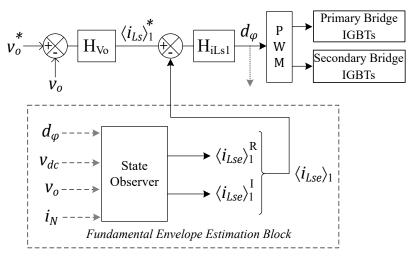

| 3.2  | Control scheme for dual loop control of DAB with HF-link current funda-                                             |    |

|      | mental envelope estimation using state observer                                                                     | 52 |

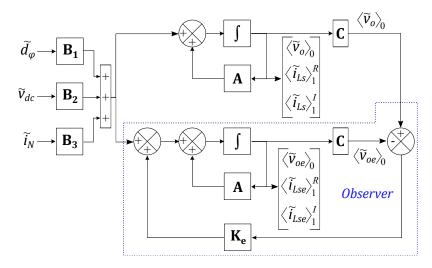

| 3.3  | Full order state observer for fundamental envelope estimation                                                       | 55 |

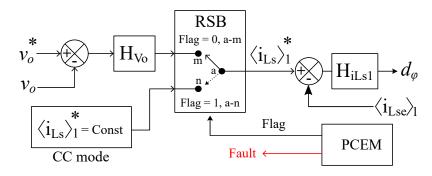

| 3.4  | Fundamental harmonic control with peak current envelope monitoring                                                  | 57 |

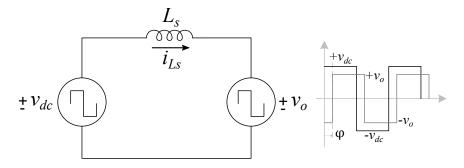

| 3.5  | DAB waveforms during one switching period                                                                           | 58 |

| 3.6  | Proposed peak current envelope monitoring (PCEM) scheme                                                             | 59 |

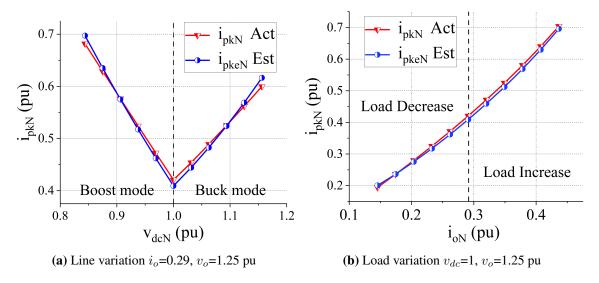

| 3.7  | Comparison plot of actual $i_{pkN}$ and estimated $i_{pkeN}$                                                        | 60 |

| 3.8  | Power transfer between two square wave AC sources                                                                   | 60 |

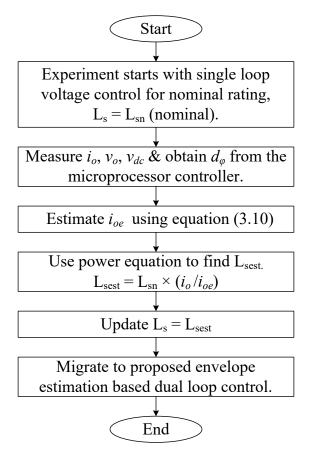

| 3.9  | Parameter identification scheme (PIS) flowchart                                                                     | 62 |

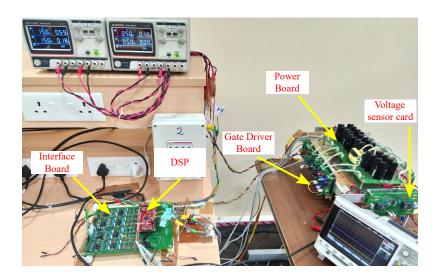

| 3.10 | Hardware Prototype                                                                                                  | 63 |

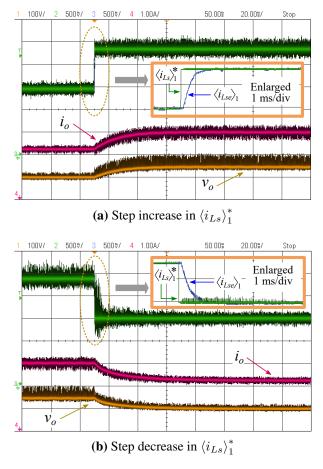

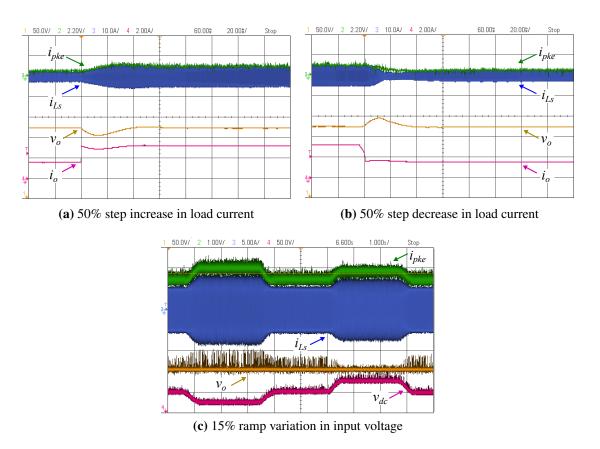

| 3.11 | Experimental results showing current tracking capability with only inner                                            |    |

|      | current loop being functional. Top trace: $\langle i_{Ls} \rangle_1^*$ and $\langle i_{Lse} \rangle_1$ (0.5 V/div), |    |

|      | 2nd trace: $i_o$ (1 A/div), Bottom trace: $v_o$ (100 V/div). Normal view - Time                                     |    |

|      | 50 ms/div. Enlarged view - Time 1 ms/div                                                                            | 65 |

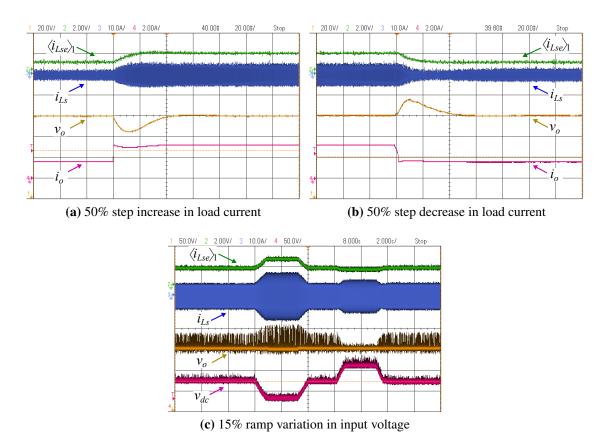

| 3.12 | Experimental results for estimation of the fundamental component enve-                                              |    |

|      | lope. Top trace: Estimated $\langle i_{Lse} \rangle_1$ (2 V/div), 2nd trace: $i_{Ls}$ (10 A/div), 3rd               |    |

|      | trace: $v_o$ (20 V/div), Bottom trace of (a) and (b): $i_o$ (2 A/div), Bottom trace                                 |    |

|      | of (c): $v_{dc}$ (50 V/div). (a) and (b): Time 20 ms/div, (c) Time 2 s/div                                          | 66 |

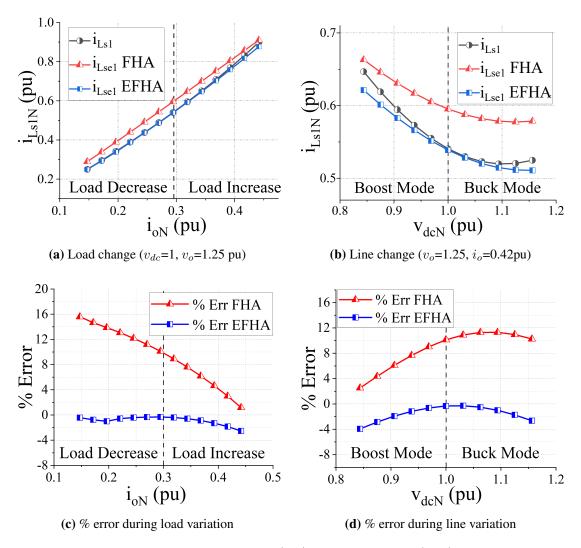

| 3.13 | Comparison of experimental $\langle i_{Ls} \rangle_1$ with estimated $\langle i_{Lse} \rangle_1$ from FHA model     |    |

|      | based observer design and EFHA model based observer design                                                          | 67 |

| 3.14 | Experimental results for peak envelope estimation. Top trace: Estimated                                  |    |

|------|----------------------------------------------------------------------------------------------------------|----|

|      | $i_{pke}$ envelope (1 V/div), 2nd trace: Actual $i_{Ls}$ (10 A/div) (a & b), (5 A/div)                   |    |

|      | (c), 3rd trace: $v_o$ (50 V/div), Bottom trace of (a) and (b): $i_o$ (2 A/div),                          |    |

|      | Bottom trace of (c): $v_{dc}$ (50 /div). (a) and (b) Time 20 ms/div, (c) Time                            |    |

|      | 1 s/div                                                                                                  | 68 |

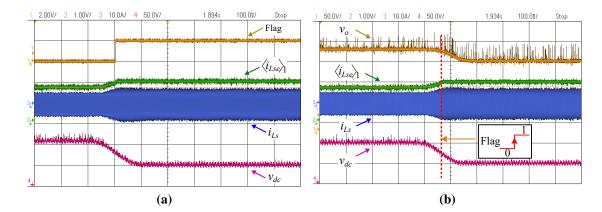

| 3.15 | Experimental results showing performance of integrated fundamental cur-                                  |    |

|      | rent control with peak current envelope monitoring. Top trace of (a): Flag                               |    |

|      | signal (2 V/div), Top trace of (b): $v_o$ (50 V/div). For both (a) and (b): 2nd                          |    |

|      | trace: $\langle i_{Lse} \rangle_1$ (1 V/div), 3rd trace: $i_{Ls}$ (10 A/div), Bottom trace: $v_{dc}$ (50 |    |

|      | V/div). Time 100 ms/div                                                                                  | 69 |

| 3.16 | Experimental results showing error in $i_{pke}$ estimation due to parametric                             |    |

|      | uncertainty. Top trace: $i_{pke}$ (1.12 V/div), Bottom trace: $i_{Ls}$ (5 A/div). Time                   |    |

|      | 10 ms/div                                                                                                | 70 |

| 4.1  | Circuit diagram of modular 1-phase type-D SST topology                                                   | 73 |

| 4.2  | Control scheme for the CMFEC stage                                                                       | 79 |

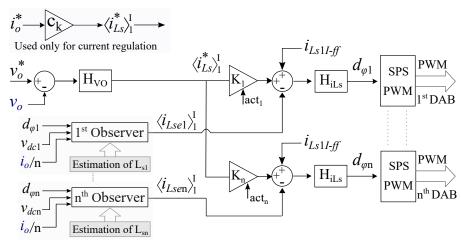

| 4.3  | Observer based power balance control in modular DAB stage                                                | 84 |

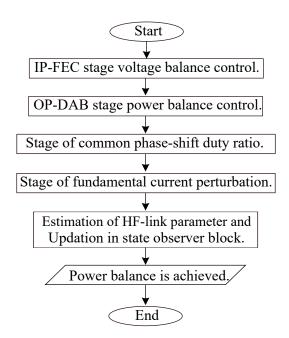

| 4.4  | Control scheme flowchart showing step by step working                                                    | 87 |

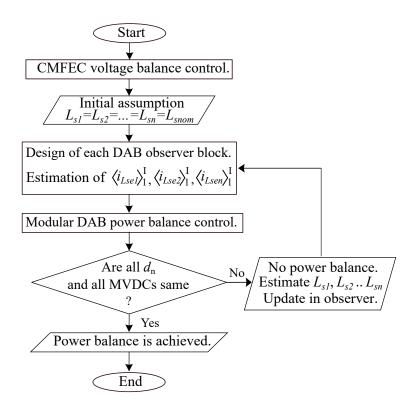

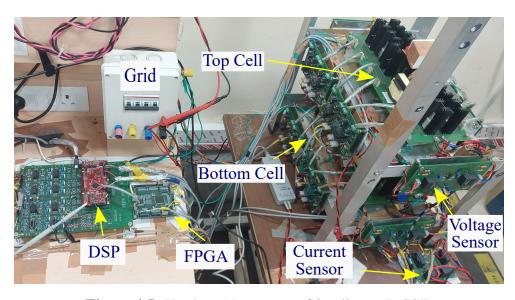

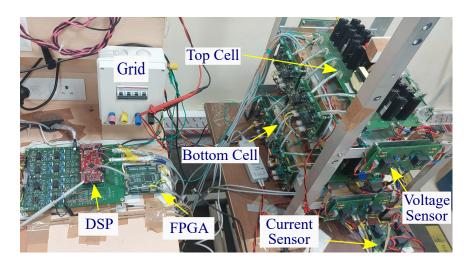

| 4.5  | Hardware Prototype of 2 cell type-D SST                                                                  | 89 |

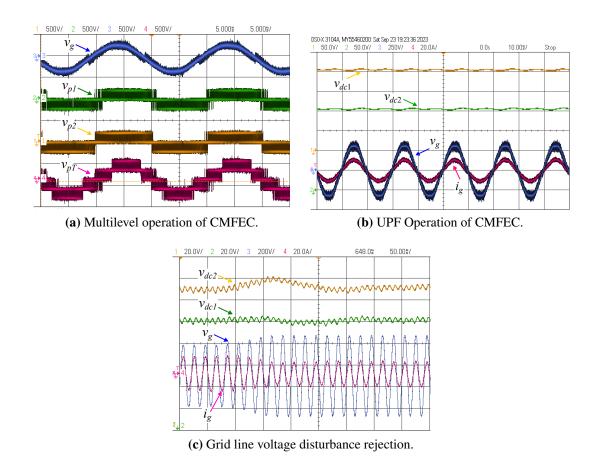

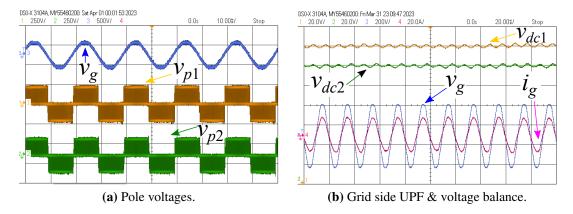

| 4.6  | Experimental results showing voltage balance control of CMFEC. (a) Top                                   |    |

|      | trace: $v_g$ (500 V/div), 2nd trace: $v_{p1}$ (500 V/div), 3rd trace: $v_{p2}$ (500 V/div),              |    |

|      | Bottom trace: $v_{pT}$ (500 V/div). (b) Top trace: $v_{dc1}$ (20 V/div), 2nd trace:                      |    |

|      | $v_{dc2}$ (20 V/div), Bottom trace: $v_g$ (200 V/div) and $i_g$ (20 A/div). (c) Top                      |    |

|      | trace: $v_{dc2}$ (20 V/div), 2nd trace: $v_{dc1}$ (20 V/div), Bottom trace: $v_g$ (200                   |    |

|      | V/div) and $i_q$ (20 A/div). Time:- (a) 5 ms/div, (b) 4 ms/div, (c) 50 ms/div.                           | 91 |

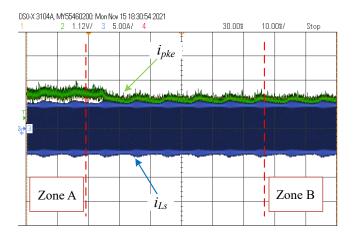

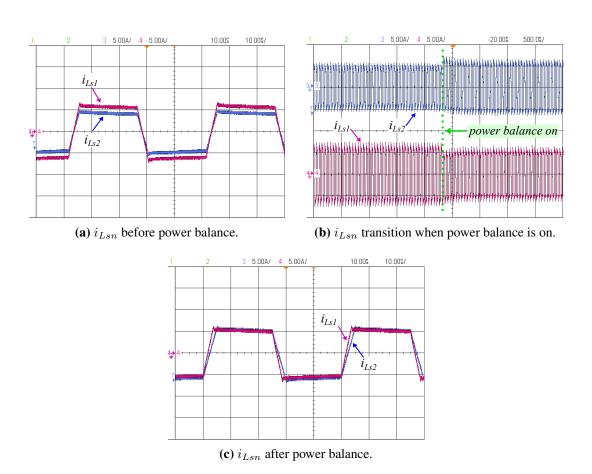

| 4.7  | Experimental results snowing DAB inductor currents during power bal-                              |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | ance. (a) $i_{Ls1}$ (5 A/div), $i_{Ls2}$ (5 A/div). (b) Top trace: $i_{Ls2}$ (5 A/div), $i_{Ls1}$ |    |

|      | (5 A/div). (c) $i_{Ls1}$ (5 A/div), $i_{Ls2}$ (5 A/div). Time:- (a) and (c): 10 $\mu$ s/div,      |    |

|      | (b) 500 μs/div                                                                                    | 92 |

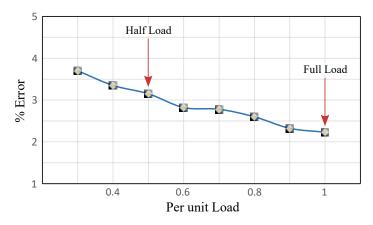

| 4.8  | Current sharing error with change in load power                                                   | 93 |

| 4.9  | Experimental results during load disturbance. (a) & (c) Top trace: $v_o$ (100                     |    |

|      | V/div), 2nd trace: $i_o$ (3 A/div), 3rd trace: $i_{Ls1}$ (10 A/div), Bottom trace:                |    |

|      | $i_{Ls2}$ (10 A/div). (b) Zoomed view of $i_{Ls1}$ and $i_{Ls2}$ shown in (a) with their          |    |

|      | oscilloscope references superimposed. Upper trace: Zone Z1 of (a), Middle                         |    |

|      | trace: Zone Z2 of (a), Bottom trace: Zone Z3 of (a). Time:- (a) & (c) 20                          |    |

|      | ms/div, (b) 50 $\mu$ s/div                                                                        | 94 |

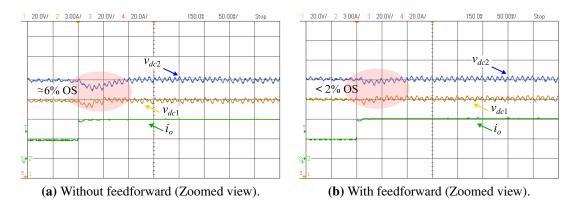

| 4.10 | Effect of Feed-forward on MVDC voltages. Top Trace: $v_{dc2}$ (20 V/div),                         |    |

|      | middle Trace: $v_{dc1}$ (20 V/div), Bottom Trace: $i_o$ (3 A/div). Time:- 50 ms/div.              | 95 |

| 4.11 | Experimental result showing $v_g$ and $i_g$ during load transient with zoomed                     |    |

|      | view. Top trace: $v_o$ (100 V/div), 2nd trace: $i_o$ (2 A/div), 3rd trace: $i_g$ (20              |    |

|      | A/div), Bottom trace: $v_g$ (500 V/div). Time:- (a) - 100 ms/div, zoomed                          |    |

|      | view - 5 ms/div                                                                                   | 96 |

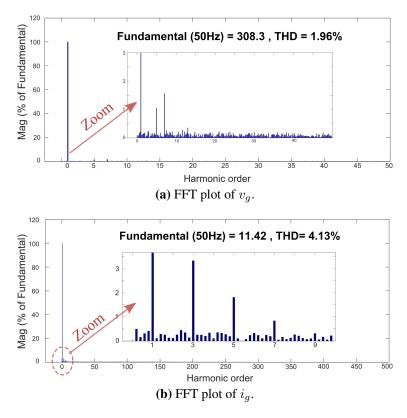

| 4.12 | FFT Plot of grid voltage and current                                                              | 97 |

| 4.13 | Experimental results showing output current regulation. (a) Top trace: $v_{dc1}$                  |    |

|      | (50 V/div), 2nd trace: $v_{dc2}$ (50 V/div), 3rd trace: $v_o$ (70 V/div), Bottom                  |    |

|      | trace: $i_o$ (3 A/div). (b) Top trace: $v_{dc1}$ (40 V/div), 2nd trace: $v_{dc2}$ (40 V/div),     |    |

|      | 3rd trace: $i_{Ls2}$ (12 A/div), Bottom trace: $i_{Ls1}$ (12 A/div). (c) Zoomed view              |    |

|      | of superimposed $i_{Ls1}$ and $i_{Ls2}$ (5 A/div). Time:- (a) 1 s/div, (b) 10 ms/div,             |    |

|      | (c) 50 μs/div                                                                                     | 98 |

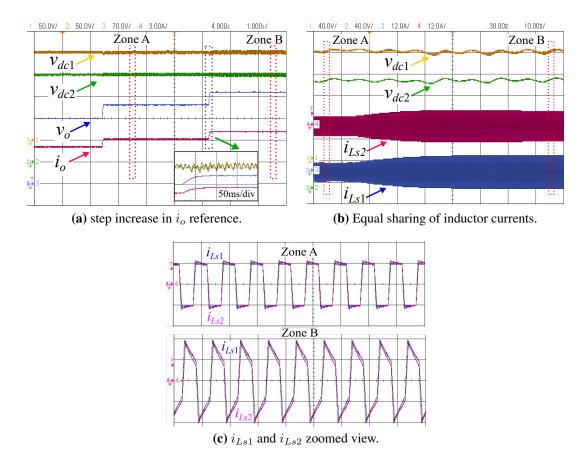

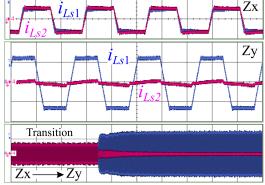

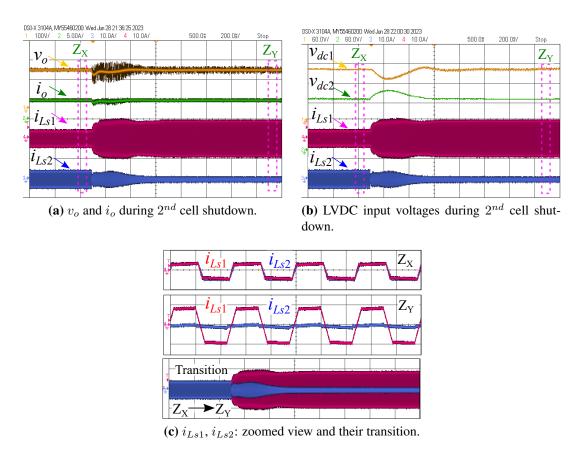

| 4.14 | Experimental results showing phase-shedding (plug-out) operation of cell                      |

|------|-----------------------------------------------------------------------------------------------|

|      | 2. (a) Top trace: $v_{dc1}$ (60 V/div), 2nd trace: $v_{dc2}$ (60 V/div), 3rd trace: $i_{Ls1}$ |

|      | (10 A/div), Bottom trace: $i_{Ls2}$ (10 A/div). (b) Top trace: $v_o$ (60 V/div),              |

|      | 2nd trace: $i_o$ (1.2 A/div), 3rd trace: $i_{Ls1}$ (10 A/div), Bottom trace: $i_{Ls2}$ (10    |

|      | A/div). (c) Zoomed view of superimposed $i_{Ls1}$ and $i_{Ls2}$ (5 A/div). Time:-             |

|      | (a) 200 ms/div, (b) 200 ms/div, (c) Zx & Zy: 20 $\mu$ s/div, Transition: 100                  |

|      | ms/div                                                                                        |

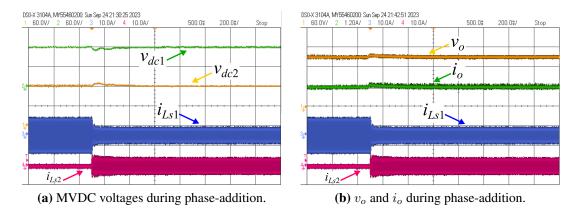

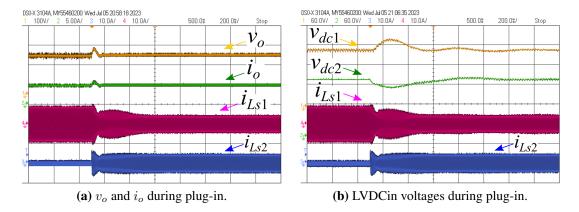

| 4.15 | Experimental result showing phase-addition (plug-in) operation of cell 2.                     |

|      | (a) Top trace: $v_{dc1}$ (60 V/div), 2nd trace: $v_{dc2}$ (60 V/div), 3rd trace: $i_{Ls1}$    |

|      | (10 A/div), Bottom trace: $i_{Ls2}$ (10 A/div). (b) Top trace: $v_o$ (60 V/div),              |

|      | 2nd trace: $i_o$ (1.2 A/div), 3rd trace: $i_{Ls1}$ (10 A/div), Bottom trace: $i_{Ls2}$ (10    |

|      | A/div). Time:- (a) 200 ms/div, (b) 200 ms/div                                                 |

| 4.16 | Top trace of (a) & (b): $i_o$ (2 A/div). 2nd Trace of (a): $i_{pke1}$ and 2nd Trace           |

|      | of (b): $i_{pke2}$ (2.2 V/div). Bottom Trace of (a): $i_{Ls1}$ and Bottom Trace of (b):       |

|      | $i_{Ls2}$ (10 A/div). Time:- 20 ms/div                                                        |

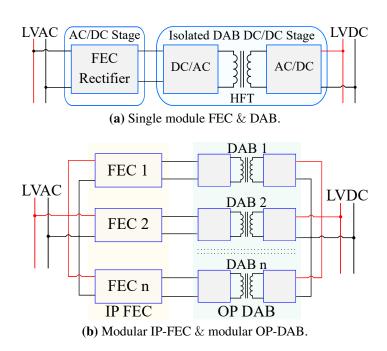

| 5.1  | Block diagram of isolated two stage LVAC-LVDC conversion system 107                           |

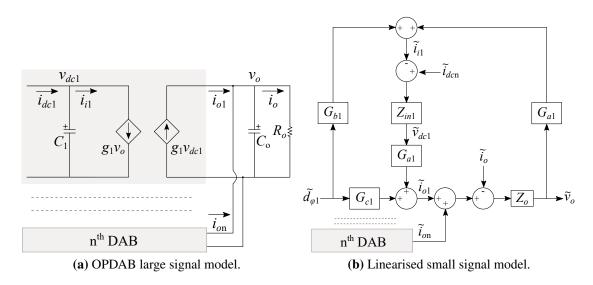

| 5.2  | Circuit diagram of modular IPFEC-OPDAB topology                                               |

| 5.3  | Proposed control scheme for the IPFEC stage                                                   |

| 5.4  | Proposed flexible power sharing control scheme for the OPDAB stage 114                        |

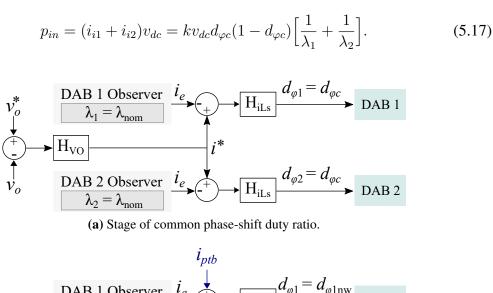

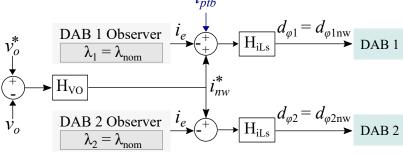

| 5.5  | FCP strategy for 2 cell IPFEC-OPDAB                                                           |

| 5.6  | Stage of FCP between DAB1 and DABn                                                            |

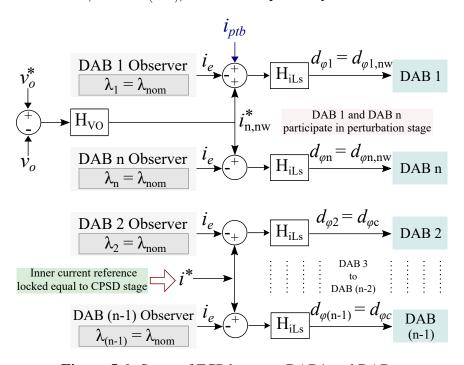

| 5.7  | Flowchart showing implementation steps of the control scheme                                  |

| 5.8  | Experimental Prototype                                                                        |

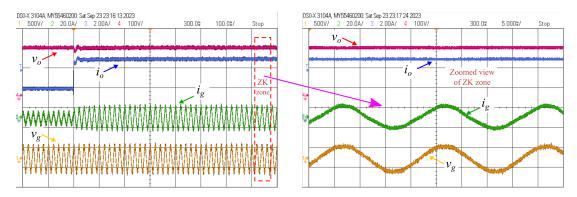

| 5.9  | Experimental results showing voltage balance control of IP-FEC. (a) Top                   |     |

|------|-------------------------------------------------------------------------------------------|-----|

|      | trace: $v_g$ (500 V/div), 2nd trace: $v_{p1}$ (250 V/div), Bottom trace: $v_{p2}$ (250    |     |

|      | V/div). (b) Top trace: $v_{dc1}$ (20 V/div), 2nd trace: $v_{dc2}$ (20 V/div), Bottom      |     |

|      | trace: $v_g$ (200 V/div) and $i_g$ (20 A/div). Time:- (a) 10 ms/div, (b) 20 ms/div.       | 121 |

|      |                                                                                           |     |

|      |                                                                                           |     |

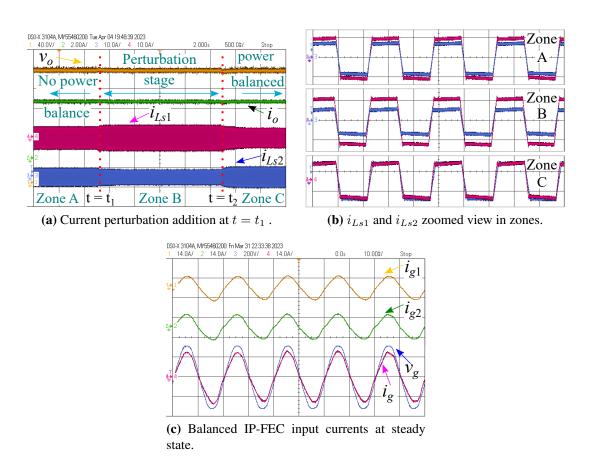

| 5.10 | Experimental results showing fundamental current perturbation based power                 |     |

|      | balance control. (a) Top trace: $v_o$ (40 V/div), 2nd trace: $i_o$ (2 A/div), 3rd         |     |

|      | trace: $i_{Ls1}$ (10 A/div), Bottom trace: $i_{Ls2}$ (10 A/div). (b) Zoomed view of       |     |

|      | $i_{Ls1}$ and $i_{Ls2}$ shown in (a) with their oscilloscope references superimposed.     |     |

|      | Upper trace: Zone A of (a), Middle trace: Zone B of (a), Bottom trace:                    |     |

|      | Zone C of (a). (c) Top trace: $i_{g1}$ (14 A/div), 2nd trace: $i_{g2}$ (14 A/div), Bot-   |     |

|      | tom trace: $v_g$ (200 V/div) and $i_g$ (14 A/div). Time:- (a) 500 ms/div, (b) 20          |     |

|      | $\mu$ s/div, (c) 10 ms/div                                                                | 122 |

|      |                                                                                           |     |

|      |                                                                                           |     |

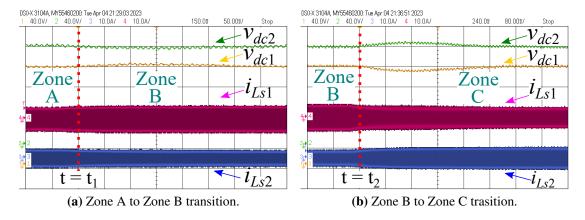

| 5.11 | Experimental results showing impact of current perturbation and compen-                   |     |

|      | sation on input LVDC voltages. (a) and (b) Top trace: $v_{dc2}$ (40 V/div), 2nd           |     |

|      | trace: $v_{dc1}$ (40 V/div), 3rd trace: $i_{Ls1}$ (10 A/div), Bottom trace: $i_{Ls2}$ (10 |     |

|      | A/div). Time:- (a) 50 ms/div, (b) 80 ms/div                                               | 124 |

|      |                                                                                           |     |

|      |                                                                                           |     |

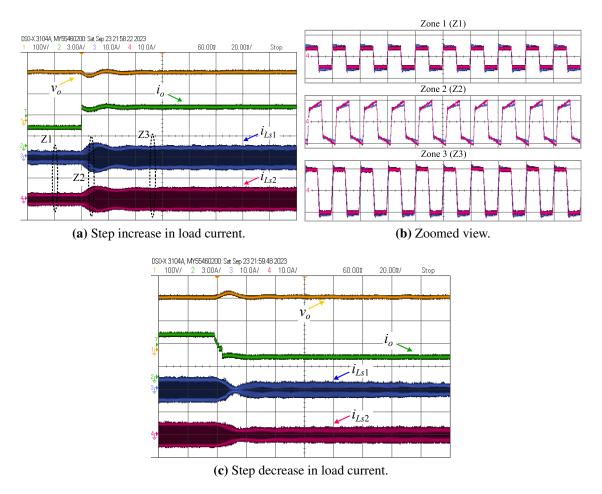

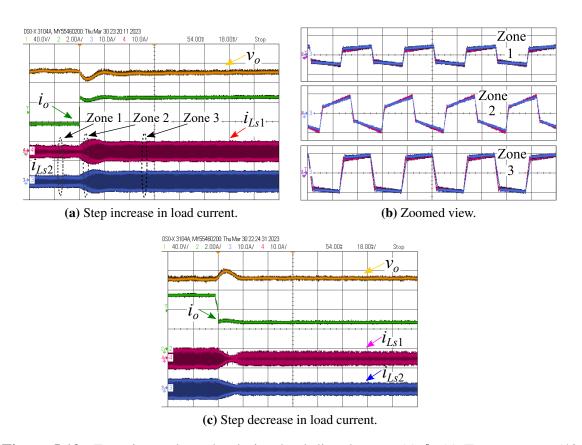

| 5.12 | Experimental results during load disturbance. (a) & (c) Top trace: $v_o$ (40              |     |

|      | V/div), 2nd trace: $i_o$ (2 A/div), 3rd trace: $i_{Ls1}$ (10 A/div), Bottom trace:        |     |

|      | $i_{Ls2}$ (10 A/div). (b) Upper trace: Zone 1, Middle trace: Zone 2, Bottom               |     |

|      | trace: Zone 3. Time:- (a) & (c) 18 ms/div, (b) 20 $\mu$ s/div                             | 125 |

|      |                                                                                           |     |

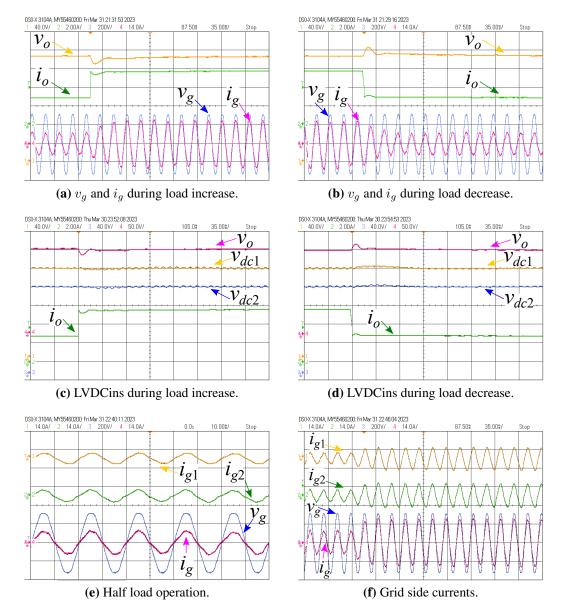

| 5.13 | Experimental results showing $v_g$ , $i_g$ , $i_{g1}$ , $i_{g2}$ , $v_{dc1}$ and $v_{dc2}$ during 50% step |     |  |

|------|------------------------------------------------------------------------------------------------------------|-----|--|

|      | load transient. (a) and (b) Top trace: $v_o$ (40 V/div), 2nd trace: $i_o$ (2 A/div),                       |     |  |

|      | 3rd trace: $v_g$ (200 V/div), Bottom trace: $i_g$ (14 A/div). (c) and (d) Top                              |     |  |

|      | trace: $v_o$ (50 V/div), 2nd trace: $v_{dc1}$ (40 V/div), 3rd trace: $v_{dc2}$ (40 V/div),                 |     |  |

|      | Bottom trace: $i_o$ (2 A/div). (e) and (f) Top trace: $i_{g1}$ (14 A/div), 2nd trace:                      |     |  |

|      | $i_{g2}$ (14 A/div), Bottom trace: $v_g$ (200 V/div) and $i_g$ (14 A/div). Time:- (a),                     |     |  |

|      | (b), (c), (d), (f) 35 ms/div. (e) 10 ms/div                                                                | 126 |  |

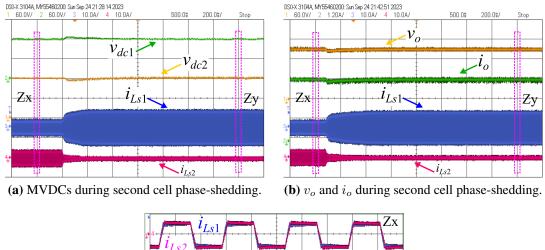

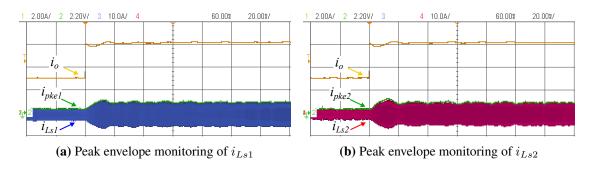

| 5.14 | Experimental results showing controlled zero power sharing (phase shed-                                    |     |  |

|      | ding) for cell 2. (a) Top trace: $v_o$ (100 V/div), 2nd trace: $i_o$ (5 A/div) , 3rd                       |     |  |

|      | trace: $i_{Ls1}$ (10 A/div), Bottom trace: $i_{Ls2}$ (10 A/div). (b) Top trace: $v_{dc1}$                  |     |  |

|      | (60 V/div), 2nd trace: $v_{dc2}$ (60 V/div) , 3rd trace: $i_{Ls1}$ (10 A/div), Bottom                      |     |  |

|      | trace: $i_{Ls2}$ (10 A/div). (c) Zoomed view of superimposed $i_{Ls1}$ and $i_{Ls2}$ (10                   |     |  |

|      | A/div). Time:- (a) & (b) 200 ms/div, (c) 20 $\mu$ s/div                                                    | 127 |  |

| 5.15 | Experimental results showing controlled phase addition of cell2. (a) Top                                   |     |  |

|      | trace: $v_o$ (100 V/div), 2nd trace: $i_o$ (5 A/div). (b) Top trace: $v_{dc1}$ (60                         |     |  |

|      | V/div), 2nd trace: $v_{dc2}$ (60 V/div). 3rd trace of (a) & (b): $i_{Ls1}$ (10 A/div),                     |     |  |

|      | Bottom trace of (a) & (b): $i_{Ls2}$ (10 A/div). Time:- (a) and (b) 200 ms/div                             | 128 |  |

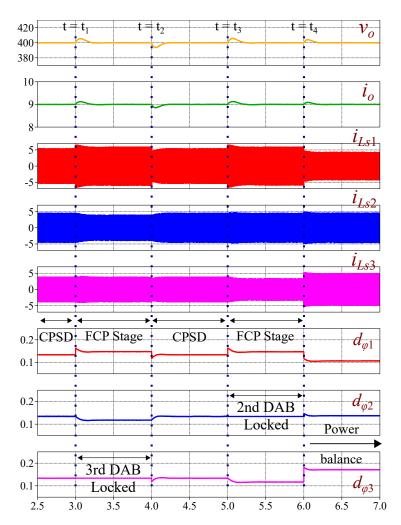

| 5 16 | Simulation waveforms for three cell                                                                        | 129 |  |

## **List of Tables**

| 1.1 | Comparison of SST with LFT                                          | 6  |

|-----|---------------------------------------------------------------------|----|

| 1.2 | Broad categorisation based on control strategy                      | 18 |

| 2.1 | Simulation Parameters with 3 cells                                  | 41 |

| 2.2 | Simulation Parameters                                               | 45 |

| 3.1 | Comparison of control schemes                                       | 51 |

| 3.2 | System Parameters                                                   | 64 |

| 3.3 | $i_{pke}$ estimation error in zones                                 | 70 |

| 4.1 | Comparison of control schemes for modular SST in ISOP configuration | 76 |

| 4.2 | Experiment Parameters                                               | 90 |

| 4.3 | Bandwidth of sensors used in this work                              | 90 |

| 5.1 | System Parameters                                                   | 21 |

## **Abbreviations**

SST Solid State Transformer

HFAC-L High Frequency AC Link

CMFEC Cascaded Multilevel Front End Converter

DAB Dual Active Bridge

HF-Link High Frequency Link

ISOP Input Series Output Parallel

MVAC Medium Voltage AC

MVDC Medium Voltage DC

LVDC Low Voltage DC

HBW High Bandwidth

GA Generalised Average

SPS Single Phase Shift

THD Total Harmonic Distortion

IPOP Input Parallel Output Parallel

IPFEC Input Parallel Front End Converter

OPDAB Output Parallel Dual Active Bridge

## **Chapter 1**

## Introduction

#### 1.1 Background

For the last couple of decades, combating global warming has been the guiding philosophy behind rethinking and reforming the power sector. The 2015 Paris Agreement sets a long-term goal, aiming to limit the rise in global mean temperature by 1.5°C [1], which would significantly mitigate the impacts of climate change. The agreement stresses on stringent emission reductions with the ultimate aim of achieving net-zero emission globally by the middle of this century. Many countries are making significant strides in this direction by adopting more and more green energy sources also known as renewable energy resources

Figure 1.1: Renewable energy (solar and wind) installed capacity.

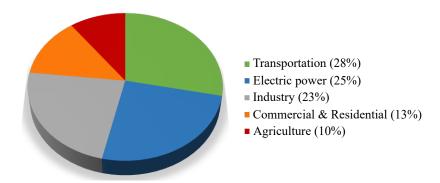

**Figure 1.2:** Emission from various sectors.

(RER) by implementing various policies and regulations. Fig. 1.1 depicts the increment in total solar and wind energy installed capacity of India and EU [2, 3, 4].

The green house gas emission from power generation and transportation sector combined is nearly 53% as shown in Fig. 1.2 [5]. The decarbonization of transport sector is expected to be a pivotal factor in accomplishing these objectives. New policies by the governments can serve as catalysts for the evolution of green transportation by mandating the widespread adoption of electric vehicles (EV). The actual and projected number of EV unit sales of this decade are highlighted in Fig. 1.3 [6, 7]. Netherlands, France, India are few examples who have announced their plans to work towards zero-emission vehicles by culminating sales of internal combustion engine vehicles by 2025, 2030 and 2040 respectively. Hence the EV market is poised to go through a substantial change soon.

**Figure 1.3:** Projected electric vehicle (EV) sale for this decade.

Figure 1.4: Power distribution system with increased penetration of RERs, BESS, EVs.

The adoption of distributed energy resources (DERs), EVs and BESS in the active distribution networks is increasing rapidly. These are expected to increase further for achieving the net-zero emission goal. A block diagram showing the increased penetration of green energy sources and loads in the modern day distribution network is shown in Fig. 1.4. The increasing integration of DERs into the conventional grid creates new challenges due to their intermittent nature. Similarly, the incorporation of EV charging stations (EVCS) into the conventional grid can give rise to various challenges, primarily due to grid-to-vehicle (G2V) and vehicle-to-grid (V2G) bidirectional charging and discharging functionalities of EVs. Key challenges are power quality issues, harmonic pollution and fluctuation in point of common coupling (PCC) voltage. To meet these emerging requirements on the distribution network, a component that needs significant renovation is the distribution transformer.

Distribution transformer is a crucial component in the distribution system. Its main objective of is to lower the high voltage to a safe level by providing galvanic isolation that can be safely utilized by residential and commercial end-users such as homes, industries and other organizations. Isolation serves to safeguard human users, protect the low voltage circuitry from higher voltages and enhance the circuit's immunity to unwanted noise.

In India, the standard voltage rating of distribution transformers is typically 11 kV or 33 kV medium voltage AC (MVAC) / 415V (3-phase) and 240V (1-phase) low voltage AC (LVAC). The nominal line frequency is 50 Hz. Henceforth, throughout this thesis the distribution transformer will be referred to as the line frequency transformer (LFT). The LFTs can be 1-phase or 3-phase. 1-phase transformer caters to residential and small commercial properties. Meanwhile, 3-phase transformers are used for bigger establishments like factories and commercial buildings. This technology has survived for more than 100 years since its inception because of its superior reliability and exceptional efficiency. However, the LFT is a passive component which is not suitable for rapidly changing load requirements with its on-load tap changer (OLTC) mechanism. These conventional transformers are also bulky and often cooled with oil having potential risk on environment. They also lack control features such as tight voltage regulation, power factor correction, fault current limitation, reactive power compensation and integration of distributed renewable energy resources. These challenges can be addressed by replacing the LFT with a smart energy router equipped with intelligent capabilities to effectively manage and regulate the flow of power. Solid state transformer (SST) is the best candidate which has the capability to overcome these limitations.

#### 1.2 The Solid State Transformer

The fundamental aim of a SST is to achieve voltage transformation using high-frequency isolation, which can result in reduced volume and weight compared to LFT. Solid state

transformers are also commonly known as power electronic transformer (PET), power electronic traction transformer (PETT) and smart transformer depending on its application [8, 9, 10, 11, 12, 13]. A SST based future grid system is depicted in Fig. 1.5. It produces an additional low voltage DC (LVDC) bus to which the DERs, EV charging stations and BESS can be directly integrated.

**Figure 1.5:** Envisioned future distribution grid with SST.

#### 1.2.1 Comparison of SST with LFT

The conventional LFT exhibits several strengths over the SST, including higher efficiency, better reliability, cost-effectiveness and higher overloading capacity [14]. Despite the aforementioned advantages, the conventional transformer experiences certain drawbacks. In LFT, the voltage transformation ratio is adjusted with OLTC. Over its lifetime, the contacts of OLTC can undergo wear and tear due to the thermal and mechanical stresses. The load voltage regulation is poor due to the sluggish response time of these mechanical devices. In SST, the voltage and frequency are controlled by power electronic converters whose response time is much faster. Due to this fast response, it can limit fault current in a controllable manner by isolating the faults quickly. High switching frequency operation is also

**Table 1.1:** Comparison of SST with LFT.

| Parameter                     | Line frequency transformer | Solid state transformer |

|-------------------------------|----------------------------|-------------------------|

| Voltage ratio                 | Adjustable by OLTC         | Controllable            |

| Frequency ratio               | Fixed                      | Controllable            |

| Power factor correction       | No                         | Yes                     |

| Unwanted harmonic suppression | No                         | Yes                     |

| Voltage regulation            | Poor                       | Tight                   |

| Fault current limitation      | No                         | Yes                     |

| Swell and sag suppression     | No                         | Yes                     |

| Smart energy routing          | No                         | Yes                     |

| DER and BESS integration      | No                         | Yes                     |

| Reliability                   | High                       | Low                     |

| Efficiency                    | High                       | Low                     |

| Cost                          | Low                        | High                    |

| Weight                        | High                       | Low                     |

| Volume                        | High                       | Low                     |

the main reason for achieving improved power density of SST compared to LFT [15].

Unlike SST, the LFT requires installation of additional shunt active filters, STATCOM, UPQC connected at the point of common coupling (PCC) for power factor correction, harmonic current filtering and improving power quality [16]. The strengths and weaknesses of SST are summarized in Table. 1.1. Given the advantages of SST over LFT, it can emerge as a more viable solution for achieving more compact and better integrated microgrid system.

Microgrid based on SST facilitates controlled bidirectional power flow between main grid-microgrid, microgrid-microgrid (inter-microgrid) and rest of the distribution networks because of the possibility of seamless reverse power flow. Hence SST can work as a smart grid enabler [17]. It also supports information exchange between each element of the distri-

Figure 1.6: Power flow between main grid-microgrid and microgrid-microgrid.

bution system by communication lines. This is presented in Fig. 1.6. The interphase power transfer is also possible in SST due to the availability of a common LVDC bus. However, it is important to note that not all categories of SSTs are suitable for microgrid applications, especially when it comes to meet the requirement of providing all the essential ancillary services.

**Figure 1.7:** Types of SST topology based on power conversion stages.

#### 1.2.2 SST Topological Configurations

There are several variants of SST topology. They are broadly categorized into Type A, Type B, Type C and Type D as shown in Fig. 1.7 [16, 18]. The Type A SST topology is a single-stage SST topology which involves direct MVAC-LVAC power conversion with high frequency link (HF-link) isolation. Type A SST offers low cost, high efficiency, and light weight solution due to usage of less components and simple configuration. The Type B and Type C SST are two-stage topologies. The two power conversion stage for Type B SST are MVAC- LVDC and LVDC-LVAC. Similarly that for Type C SST are MVAC-MVDC and MVDC-LVAC. The Type D SST topology is a three stage SST topology which consists of three power conversion stages: MVAC-MVDC, MVDC-LVDC and LVDC-LVAC. Among the above four types only Type B and Type D SST topologies allows integration of DERs, EV charging stations and BESS due to the availability of the LVDC bus. Hence, only Type B and Type D SST are suitable for smart grid application. The Type B configuration may not be well-suited for high voltage operation due to the challenges in ensuring zerovoltage switching (ZVS) over a very wide MVAC voltage range. In some cases the circuit configuration of two-stage SST and three-stage SST are same. The only difference being in two-stage SST, the MVDC link electrolytic capacitor is replaced by a small AC capacitor to reduce the capacitor size. Hence, the second harmonic ripple power in a 1-phase system gets transmitted from the MVDC side to the LVDC side. For a 1-phase system application, a large electrolytic capacitor is still required at the LVDC bus to suppress this transmitted second harmonic component from MVDC side. For the 3-phase application, as all the output sides of 3-phases are integrated to a common LVDC bus, the total second harmonic ripple power will add up to zero due to the phase differences in 3-phases. However, due to the absence of intermediate MVDC link in Type B two-stage SST, there exists a direct coupling between MVAC and LVDC which can cause the propagation of disturbances from one side to the other. Due to these reasons, the Type D configuration is commonly favoured

because it includes two DC-links, which offer high flexibility and versatility for a wide range of applications. The intermediate MVDC link capacitor prevents the disturbance to propagate from MVAC to LVDC by acting as an stiff energy buffer. A consequence of this is a weak line-load dynamic coupling which facilitates good disturbance rejection capability. It is also observed that the three-stage SST gives superior voltage regulation, fault current limitation, protection, and power factor performance than one or two stage SST [19]. Hence, Type D SST is one of the most preferred choice for many academic as well as industrial applications such as: ABB, GE, EPRI, UNIFLEX and FREEDM system centre [20, 21, 22, 23]. Due to the above mentioned reasons, in this thesis the Type D SST topology is considered.

## 1.2.3 Modular Topologies

The Type D SST topology can be further categorized into two types: non-modular and modular Type D SST. The non-modular architecture utilizes high-voltage wide-bandgap semiconductor devices for high blocking voltage and high power requirements [24, 25]. Due to the single cell structure the number of switches, DC-link capacitors, HF-link magnetics, gate drivers and sensors required is lower compared to modular structure. However, it lacks scalability which may hamper its suitability for microgrid applications. Additionally, these high-voltage wide-bandgap semiconductor switches have limited commercial availability. Modular SST architecture have several advantages over non-modular structure. Modularity improves reliability due to presence of additional redundancy. Modularity enables reduction in manufacturing costs by leveraging standardized, commercially available low-voltage semiconductor devices. It reduces the electromagnetic interference emission by reducing the dv/dt transition. Through the utilization of modular multilevel converters in a modular SST, it becomes possible to synthesize multilevel waveforms, which in turn, helps minimizing the size of the required filter elements. Additionally, it facilitates

**Figure 1.8:** Four types of series-parallel connected modular power conversion systems.

easy scalability by providing flexibility to increase power and voltage levels as needed. Modularity also simplifies transportation and installation in challenging locations such as off-shore transmission applications. Hence, considering the reasons mentioned above, the modular Type D SST topology has been chosen for investigation in this thesis to explore its control strategy.

Fig. 1.8 shows four types of modular power conversion systems, these are, ISOS (input-series-output-series), ISOP (input-series-output-parallel), IPOS (input-parallel-output-series) and IPOP (input-parallel-output-parallel) [26, 27]. ISOS configuration is used for application requiring high input voltage and high output voltage. ISOP modular structure is suitable for SST in distribution system application. Many converters can be connected in series at the input MVAC side for high input voltage blocking and in parallel at the output LVDC side for high load current rating. ISOP configuration is also suitable for traction onboard application. IPOS configuration is used for high input current and high output voltage application. Similarly, IPOP configuration is well suited for the high input current and large

output current application. In this thesis the development of control strategies for the modular ISOP Type D and modular IPOP Type D topologies is focused, aiming to achieve the desired control objectives. The next step involves selecting the suitable converter topology for each of the three stages of the modular Type D topology.

### 1.2.4 Stage-wise Topological Choices

The four feasible multilevel MVAC-MVDC topologies are neutral point clamped, flying capacitor converter, modular multilevel converter (MMC) and cascaded multilevel front end converter (CMFEC) [10, 19]. The first two are not suitable solutions as they do not facilitate easy scalability which is essential for plug-in and plug-out operation. MMC and CMFEC are the two most promising solutions for MVAC-MVDC conversion stage. While MMC offers the advantage of a single MVDC link for integrating MVDC sources/loads, it comes with drawbacks such as a very complex control system and the need for a bulky DC-side filter compared to CMFEC which significantly increases the cost. The CMFEC stands out as the most promising topology because of the simplicity of its modulation and control system. Hence, for the first stage of modular ISOP Type D SST, the CMFEC converter topology has been chosen in this research work.

In the second MVDC-LVDC stage, the converter houses the HF-link isolation transformer. This stage is regarded as one of the most challenging stages due to the high current on the LV side and the high voltage on the MV side. There are various feasible topology for the second stage. These are series LC resonsant converter (SRC), LLC resonant converter, dual half bridge (DHB) converter, dual active bridge converter (DAB), DAB with SRC, quad active bridge (QAB) converter [10, 19]. Out of these, the non-resonant DAB converter is selected in the second stage for this research work because it offers advantages such as: easily controllable bidirectional power flow by controlling the phase shift and a simple single phase shift (SPS) modulation scheme. Moreover, in DAB the efficiency can

be improved by adopting optimized modulation strategy like dual phase shift control (DPS) or triple phase shift control (TPS) or extended phase shift control (EPS).

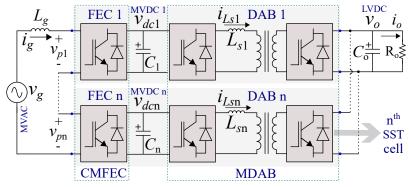

The third stage is the LVDC-LVAC conversion stage for the load consumption side. A simple voltage source inverter is selected for the third stage. The circuit diagram of the selected modular ISOP Type D SST topology is shown in Fig. 1.9.

**Figure 1.9:** Selected three stage modular ISOP Type D SST topology.

## 1.3 Motivation of the Thesis

DAB is the central power processing unit of SST. It consists of two H-bridges, where both primary and secondary H-bridges are modulated at 50% duty cycle. The phase-shift-duty ratio, denoted by  $d_{\varphi}$ , between the two H-bridges is the control input to the plant which

controls the power flow. A state of art literature review on the control methods of a single cell DAB as well as in the context of modular SST is discussed subsequently.

#### 1.3.1 Literature Review

DAB provides galvanic isolation through its HF-link consisting of an inductor and transformer. The magnitude of power transfer in the converter is predominantly governed by the fundamental component of this current. Meanwhile, its peak component dictates the over-current saturation boundary of the HF-link magnetic core. Hence, the information of this purely AC HF-link current is very important, which is missing while performing the single outer voltage loop control of DAB [28, 29, 30, 31]. The most widely used method for control of DAB is the dual loop control, which comprises an outer voltage loop and an inner current loop. The key features of the dual loop control strategy are: power flow control, limitation of current to provide over-current protection and improvement of the dynamic response of converter during load and line disturbances. The block diagram of dual loop control of DAB is shown in Fig. 1.10.

Figure 1.10: Dual loop control of DAB converter.

Dual loop control is proposed for the current stress optimization and efficiency improvement by deriving the optimal phase-shift-duty in [32, 33]. Predictive current mode control of DAB is presented in [34], which protects the transformer from saturation by measuring and sampling the HF-link current. A predicted peak-current based dual loop analog control of DAB is presented in [35] to achieve fast dynamic response for More

electric aircraft application. A double band analog current control method to avoid the risk of transformer saturation is proposed in [36] based on feed-forward compensation by measuring the HF-link current. Active saturation mitigation of DAB by detecting the variation of HF-link current slope near the saturation boundary is proposed in [37]. It depends on the measurement of the terminal DC-link current of DAB using current shunt resistor. Decoupled current control approach is employed in [38, 39], based on state observer to estimate and control the real and reactive power component independently. [38] requires HF-link AC current information, where as, [39] requires terminal DC link current information, which are obtained using different measurement techniques. However, these current measurements require high bandwidth current sensor, high sampling ADC and high sampling frequency. These challenges can be addressed by adopting current sensorless control utilizing estimation technique. The requirement of HF-link current estimation is discussed in detail in the subsequent subsection.

## 1.3.2 Requirement of HF-link Current Estimation

In order to implement dual loop control scheme, it is required to have the information of the HF-link current or the terminal DC-link current. The HF-link current and the terminal DC-link current are denoted by  $i_{hfac}$  and  $i_{tdc}$  respectively as shown in the Fig. 1.11. The HF-link current is a purely AC current whose fundamental frequency component is the switching frequency. The terminal DC-link current is a DC current with high ripple at twice the switching frequency. Fig. 1.11 illustrates the possible positions, denoted as P1, P2, and P3, where current sensors can be installed to measure the required current.

There are several types of current sensors/transducers based on their working principles and the technology used [40, 41]. For high power and high voltage application isolated current sensor is used. Few examples of commercially available isolated current sensors are shown in Fig. 1.12. The widely used method for measuring the terminal DC link current

is the combination of a shunt resistor and an optical isolation amplifier [37]. This approach offers several advantages, including cost-effectiveness, ease of handling and mounting. It is particularly well-suited for low current measurement. However, for applications involving high current, the shunt system faces several challenges. Magnetic IC current sensors are single chip solution used for the measurement of current over the PCB trace. However, these sensors have limited current measurement range and limited bandwidth. Rogoswski coil current sensing method features a thin and flexible design due to no use of mangetic core. It requires an integrator for the integration of output signal to obtain the actual current value. This integration process can introduce errors and inaccuracies in the measurement. Due to the use of air core it can also get affected by nearby magnetic field.

There are several types of magnetic core based current sensing methods, such as: current transformer, open loop Hall effect and closed loop Hall effect current sensor. The closed-loop Hall effect current sensor is favoured for high-current measurement applications. Its utilization of feedback compensation coil allows it to operate nearly at zero flux, resulting in significantly improved performance and accuracy. However, these are expensive and bulky. The magnetic core necessitates dedicated mounting space. Integrating this sensor on the busbar structure (as shown in positions P1, P3 of Fig. 1.11), may impede the goal of achieving a compact laminated busbar design to minimize stray inductance [42, 43].

Figure 1.11: DAB circuit showing position of current sensor placement.

Apart from the HBW current sensor requirement, high sampling rate ADC is also essential to sample the current for digital control implementation. The sampling frequency must be nearly five to ten times greater than the switching frequency for signal processing, which imposes a limitation on the operating switching frequency of the DAB converter.

Figure 1.12: Few examples of isolated current sensors.

These above mentioned reasons stand as the principal motivation for implementing current sensorless control by estimation of the HF-link current.

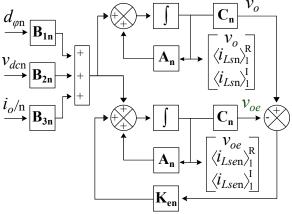

### 1.3.3 Preservation of HF-Link Current Dynamics

Estimation of the HF-link current requires a well-defined dynamic model of the plant. Several modeling methods have been proposed to approximate the nonlinear and time-varying characteristics, in order to arrive at a linear, time-invariant representation. The three primary methodologies for modeling DAB converters are: discrete time modeling, reduced-order modeling and generalized average (GA) modeling. A full-order discrete-time modeling approach can have good accuracy and it is used for resonant converters. However, a simple continuous-time domain model is typically preferred due to its ability to offer more physical insights of the system. The reduced order model based on state space average modeling approach is commonly used for DAB. However, it does not include the dynamics of the HF-link current and hence does not provide any information regarding the HF-link current [44], [45].

In DAB, input voltage variation causes the HF-link current to transit from a trapezoidal shape to a more peaky waveform. When designing the inductor, its energy storing capability is determined by the peak current. However, as the peak current magnitude increases, the operating point moves closer to the knee region of B-H curve, which may lead to core saturation due to over-current. Estimating the HF-link current helps to gather information about its fundamental and peak magnitude. This is the reason for the estimation of HF-link current instead of the terminal DC-link current. The knowledge of the estimated fundamental current can be employed to control the active power. Besides this, monitoring the peak current aids in detecting over-current situations in the HF-link. This serves another motivation for the estimation of HF-link current with a good dynamic model which does not eliminate it as a state variable of the system. The GA modeling approach based on fun-

**Table 1.2:** Broad categorisation based on control strategy.

| Strategy | Stage | Control Input                 | Balance Objective    |  |

|----------|-------|-------------------------------|----------------------|--|

| A        | CMFEC | Equal/unequal modulation-duty | MVDC balance         |  |

|          | DAB   | Phase-shift-duty              | Power balance        |  |

| В        | CMFEC | Only equal modulation-duty    | MVDC balance         |  |

|          | DAB   | Phase-shift-duty              | Power balance        |  |

| С        | CMFEC | Only equal modulation-duty    |                      |  |

|          | DAB   | Phase-shift-duty              | MVDC & Power balance |  |

damental harmonic approximation (FHA) helps in capturing the dynamics of the HF-link current and its low frequency envelope. This thesis aims to utilize the Generalized Average (GA) model and develop an estimator which can capture the dynamics of HF-link current.

### 1.3.4 Extension of Control Scheme to Modular Structure

The adoption of the modular configuration in high-power applications is due to its numerous advantages, as discussed earlier. Nevertheless, the modular structure faces challenges arising from cell-to-cell parametric variation caused by manufacturing errors and ageing related factors. In a modular SST, the HF-link inductance of the DAB converter plays a pivotal role in governing the power flow between cells. The variation of this parameter among the cells is the primary cause of power imbalances across the different cells of the modular SST.

There are various voltage and power balance methods proposed to tackle this problem. According to the control objectives of CMFEC in the first stage and modular DAB in the second stage, the control strategies can be categorized broadly into three types, which are: Strategy A, Strategy B and Strategy C.

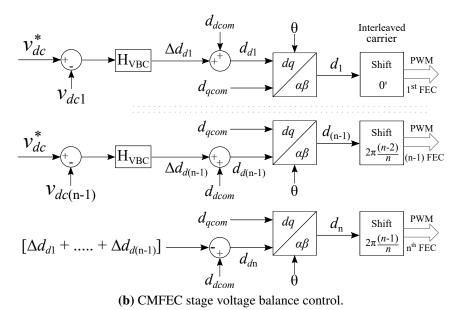

The control objectives of strategy A in CMFEC stage are: grid side unity power factor operation, regulation of summation of MVDC voltages and MVDC voltage balance [46,

47]. The role of modular DAB is to regulate the LVDC port voltage and balance cell-to-cell power. The limitation of this approach is, it requires the measurement of HF-link current or terminal DC link current using high HBW current sensors and high sampling ADCs to calculate average power for the implementation of power balance control.

Strategy B balance control approach is also proposed without measuring the HF-link current [48, 49] by modifying the active component of CMFEC duty ratio. Current sensorless power balance control strategy of SST is proposed to eliminate the use of HBW current sensor using strategy C. This method draws inspiration from the common control approach utilized for ISOP DC-DC converters [50, 51, 52]. Since modular SST is an ISOP AC-DC converter, this method is adopted by assigning a common modulation-duty cycle to all series connected FECs of CMFEC [53, 54, 55, 56]. This effectively ensures that all output parallel connected modular DAB behaves like ISOP DC-DC converter enabling power balance across the modular SST. In the modular DAB stage using the MVDC voltage balance controller the phase-shift-duty in each DAB is compensated to achieve power balance. Hence, the control objective of modular DAB is both MVDC voltage balance and cell-to-cell power balance. The CMFEC does not participate in any balance objective. It only regulates MVDC voltage summation and achieve grid side UPF operation. When it comes to control mechanism, strategy B is similar to strategy C eventually in the steady state. In both control approach, the modular DAB converter functions as equivalent to ISOP system.

Due to the possibility of only common modulation-duty in CMFEC stage in both strategy B and C control approach, it puts constraints on utilization of the full degrees of freedom provided by the topology. It does not allow cell-to-cell current control. A major drawback is its inability to provide controlled unequal power sharing capability. In modular configurations, controlled unequal power sharing can yield several advantages, particularly in facilitating phase shedding and addition operations (plug-in and plug-out operation) to enhance overall system efficiency during low load periods. Additionally, these schemes

are only applicable to ISOP configurations and they fall short in achieving power balance in IPOP configurations. The reasons mentioned above serve as the primary motivation for developing a flexible power sharing control strategy based on HF-link current estimation and parameter identification, which can be adopted for any configuration. Therefore, the broad aim of the thesis is categorized into the following.

## 1.4 Objectives of the Thesis

The objectives of this thesis are,

- Development of a HBW current sensorless control scheme for single cell DAB, which provides a direct control handle on the HF-link current fundamental envelope, enabling the control over its active power.

- Utilizing the developed control scheme, develop a control strategy to achieve the flexible power sharing of modular ISOP SST, which can offer controlled equal, unequal and zero power sharing feature.

- 3. Utilizing the developed control scheme, develop a control strategy to achieve the flexible power sharing of modular IPOP AC-DC converter for high-input-high-output current application.

- 4. Perform experimental validations of the analytical claims.

### 1.5 Thesis Outline

A pictorial representation of the thesis highlighting its key contributions and its outline is presented in Fig. 1.13. This thesis is organized in to six chapters in the following manner.

- Chapter 2 focuses on the dynamic modeling approach and modulation schemes employed for SST in this research work. This chapter covers the derivation of the low-frequency dynamic model of the CMFEC and presents its Pulse Width Modulation (PWM) scheme. Additionally, the modeling strategies of the DAB converter and its modulation strategy are also discussed.

- Chapter 3 proposes a hierarchical control scheme for a single cell DAB converter.

This control strategy focuses on regulating the fundamental and peak component of the HF-link current without using high bandwidth sensors. Relevant experimental results are presented for the validation.

- Chapter 4 presents a voltage and power control strategy for modular SST, which, in addition to enabling cell-to-cell power balance, also offers controlled flexible power sharing when needed by controlling the HF-link fundamental current component. Relevant experimental results are presented for the validation.

- Chapter 5 introduces a control strategy that achieves voltage balance and flexible power sharing for modular IPOP AC-DC converters with HF-link isolation. The UPF operation of multiple parallel cells on the grid side is performed using only one current sensor, while parameter identification is conducted through perturbation algorithm. Relevant experimental results are presented for the validation.

- **Chapter 6** concludes this thesis by summarizing its key findings and identifying several potential directions for future research.

Figure 1.13: A pictorial representation highlighting key research contributions and outline of this thesis

# Chapter 2

# Low Frequency Dynamic Model

In this chapter, the low-frequency linear dynamic model of SST is presented. The modeling process is divided into two distinct steps: AC-DC CMFEC stage and DC-DC isolation OPDAB stage, which are discussed sequentially. The primary objective of this chapter is to derive the average large signal model, the linearized small signal model and key control-input-to-state-variable transfer functions for each stages. The pulse width modulation (PWM) schemes employed in this research work are also discussed.

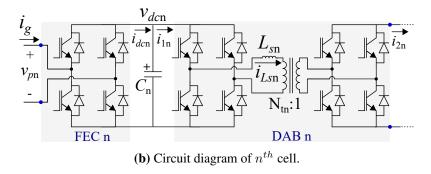

Figure 2.1: CMFEC and its AC equivalent circuit.

# 2.1 Modeling of CMFEC

The control objectives of the CMFEC stage are

- 1. To draw unity power factor from the grid.

- 2. To regulate the summation of all MVDC voltages.

- 3. To regulate and balance the individual MVDC voltage. (if MVDC voltage balance control objective is adopted in this stage Strategy A).

The circuit diagram of the CMFEC stage and its AC equivalent circuit is shown in Fig. 2.1. The dynamic equations of CMFEC averaged over a switching period are,

$$\frac{di_g}{dt} = \frac{v_g}{L_g} - \frac{r_g}{L_g} i_g - \frac{v_{pt}}{L_g},\tag{2.1}$$

$$\frac{dv_{dck}}{dt} = \frac{i_{dck}}{C_k} - \frac{i_{ik}}{C_k} = \frac{d_k i_g}{C_k} - \frac{1}{C_k} \frac{v_{dck}}{R_{ok}}, \text{ where } k = 1, 2..., n.$$

(2.2)

Here, the grid voltage, grid current, and the  $k^{th}$  cell MVDC voltage are denoted by  $v_g$ ,  $i_g$  and  $v_{dck}$  respectively. The parasitic resistance of grid interfacing inductance  $(L_g)$  is  $r_g$  and  $C_k$  is the MVDC capacitance of  $k^{th}$  cell .  $R_{ok}$  is the effective input impedance of  $k^{th}$  DAB, which behaves as a load to the  $k^{th}$  FEC. The total pole voltage  $(v_{pt})$  is given in (2.3), where,  $d_k$  is the modulation-duty ratio of  $k^{th}$  FEC module.

$$v_{pt} = \sum_{k=1}^{n} v_{pk} = \sum_{k=1}^{n} d_k v_{dck}.$$

(2.3)

The phasor diagram of CMFEC for forward and reverse power flow is shown in Fig. 2.2.  $v_g$  and  $i_g$  are required to be in phase for UPF operation. To meet this objective, the conventional vector control method is adopted. The stationary orthogonal axes  $\alpha\beta$  are

Figure 2.2: Phasor diagram of CMFEC for UPF operation.

transformed into synchronously rotating dq reference frame. It is presented in Fig. 2.3. The dynamic equations of CMFEC in dq reference frame are derived as,

$$\frac{di_{gd}}{dt} = \frac{v_{gd}}{L_g} - \frac{r_g}{L_g} i_{gd} + \omega i_{gq} - \frac{1}{L_g} \sum_{k=1}^n d_{dk} v_{dck}, \tag{2.4}$$

$$\frac{di_{gq}}{dt} = \frac{v_{gq}}{L_g} - \frac{r_g}{L_g} i_{gq} - \omega i_{gd} - \frac{1}{L_g} \sum_{k=1}^n d_{qk} v_{dck},$$

(2.5)

$$\frac{dv_{dck}}{dt} = \frac{1}{C_k} [d_{dk}i_{gd} + d_{qk}i_{gq}] - \frac{i_{ik}}{C_k}; \quad k = 1, 2..., n.,$$

(2.6)

where,  $x_d$  and  $x_q$  represent the d and q axis component of x,  $x \in [v_g, i_g, d_k]$ . The small signal model is derived by applying a small perturbation to the control input  $d_k$  in the dq domain as,

**Figure 2.3:** Stationary  $\alpha\beta$  to synchronously rotating dq reference frame transformation.

$$\tilde{d}_{dk} = d_{dk} - D_{dk},\tag{2.7}$$

$$\tilde{d}_{qk} = d_{qk} - D_{qk},\tag{2.8}$$

where, the  $\tilde{d}_{dk}$ ,  $\tilde{d}_{qk}$  are the control inputs and  $D_{dk}$ ,  $D_{qk}$  are the steady state values at the operating point of linearization. The perturbation in control input will cause deviation in the state variable x,  $x \in [v_g, i_g, v_{dck}]$ . The perturbed and steady state value of variable x are  $\tilde{x}$  and X respectively. Consequently, the linearised small signal model is derived as,

$$\frac{d\tilde{i}_{gd}}{dt} = \frac{\tilde{v}_{gd}}{L_g} - \frac{r_g}{L_g}\tilde{i}_{gd} + \omega\tilde{i}_{gq} - \frac{1}{L_g}\left[\sum_{k=1}^n \tilde{d}_{dk}V_{dck} + \sum_{k=1}^n D_{dk}\tilde{v}_{dck}\right],\tag{2.9}$$

$$\frac{d\tilde{i}_{gq}}{dt} = \frac{\tilde{v}_{gq}}{L_g} - \frac{r_g}{L_g} \tilde{i}_{gq} - \omega \tilde{i}_{gd} - \frac{1}{L_g} \left[ \sum_{k=1}^n \tilde{d}_{qk} V_{dck} + \sum_{k=1}^n D_{qk} \tilde{v}_{dck} \right], \tag{2.10}$$

$$\frac{d\tilde{v}_{dck}}{dt} = \frac{1}{C_k} [\tilde{d}_{dk} I_{gd} + D_{dk} \tilde{i}_{gd} + \tilde{d}_{qk} I_{gq} + D_{qk} \tilde{i}_{gq}] - \frac{\tilde{i}_{ik}}{C_k}, \text{ where } k = 1, 2..., n. \quad (2.11)$$

The large signal and the small signal model circuit diagram of CMFEC in dq reference frame is shown in Fig. 2.4. For the derivation of transfer functions from the small signal model, the cross coupling terms  $(+\omega \tilde{i}_{gq} \text{ and } -\omega \tilde{i}_{gd})$  are not considered as their effect will be compensated through the inclusion of decoupling feed-forward terms in the closed-loop control. The control-to-output current  $(G_{igd-ddk}, G_{igq-dqk})$ , current-to-output voltage  $(G_{vdck-igd}, G_{vdck-igq})$  and control-to-output voltage  $(G_{vdck-ddk}, G_{vdck-dqk})$  transfer functions are derived and shown as follows,

$$G_{igd-ddk}(s) = \frac{\tilde{i}_{gd}(s)}{\tilde{d}_{dk}(s)} = -\frac{V_{dck}}{sL_g + r_g}, \qquad G_{igq-dqk}(s) = \frac{\tilde{i}_{gq}(s)}{\tilde{d}_{gk}(s)} = -\frac{V_{dck}}{sL_g + r_g}.$$

(2.12)

Figure 2.4: Large signal and small signal model of CMFEC in dq reference frame.

$$G_{vdck-igd}(s) = \frac{\tilde{v}_{dck}(s)}{\tilde{i}_{gd}(s)} = \frac{D_{dk}R_{ok}}{sC_kR_{ok}+1}, \quad G_{vdck-igq}(s) = \frac{\tilde{v}_{dck}(s)}{\tilde{i}_{gq}(s)} = \frac{D_{qk}R_{ok}}{sC_kR_{ok}+1}.$$

(2.13)

$$G_{vdck-ddk}(s) = \frac{\tilde{v}_{dck}(s)}{\tilde{d}_{dk}(s)} = \frac{I_{gd}R_{ok}}{sC_kR_{ok}+1}, \quad G_{vdck-dqk}(s) = \frac{\tilde{v}_{dck}(s)}{\tilde{d}_{dq}(s)} = \frac{I_{gq}R_{ok}}{sC_kR_{ok}+1}.$$

(2.14)

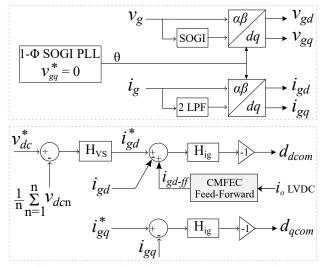

Utilizing these transfer functions, the closed loop control diagram of CMFEC is shown in Fig. 2.5. It is a dual loop control consisting of outer voltage loop and inner current loop.  $H_{vs}$  and  $H_{ig}$  represents the voltage controller and current controller for the outer loop and inner loop respectively. The feed-forward terms  $(i_{gd}C_1, i_{gq}C_1 \text{ and } v_{gd}C_2)$  are added to the inner current loop for decoupled current control. The load disturbance input of the  $k^{th}$  cell is denoted by  $i_{dtbk}$ . The actuator transfer function of  $k^{th}$  FEC  $(G_{actk})$  is given in (2.15), where,  $T_d$  is the switching period delay using Padé approximation.

$$G_{actk} = \frac{V_{dck}}{1 + sT_d}. (2.15)$$